# Memory-Centric Computing

Onur Mutlu

omutlu@gmail.com

https://people.inf.ethz.ch/omutlu

9 July 2023

IMACAW Keynote Talk @ DAC

Carnegie Mellon

# Computing is Bottlenecked by Data

## Data is Key for AI, ML, Genomics, ...

Important workloads are all data intensive

They require rapid and efficient processing of large amounts of data

- Data is increasing

- We can generate more than we can process

- We need to perform more sophisticated analyses on more data

#### Huge Demand for Performance & Efficiency

## SeanLie

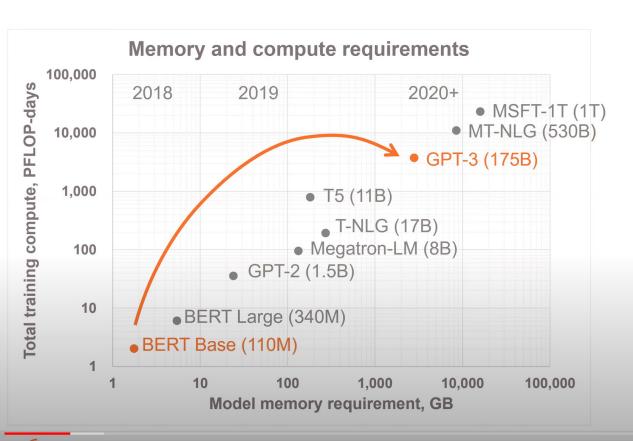

#### **Exponential Growth of Neural Networks**

1800x more compute

In just 2 years

Tomorrow, multi-trillion parameter models

### Data is Key for Future Workloads

#### **In-memory Databases**

[Mao+, EuroSys'12; Clapp+ (Intel), IISWC'15]

#### **In-Memory Data Analytics**

[Clapp+ (Intel), IISWC'15; Awan+, BDCloud'15]

#### **Graph/Tree Processing**

[Xu+, IISWC'12; Umuroglu+, FPL'15]

#### **Datacenter Workloads**

[Kanev+ (Google), ISCA'15]

#### Data Overwhelms Modern Machines

**In-memory Databases**

**Graph/Tree Processing**

## Data → performance & energy bottleneck

#### **In-Memory Data Analytics**

[Clapp+ (Intel), IISWC'15; Awan+, BDCloud'15]

#### **Datacenter Workloads**

[Kanev+ (Google), ISCA' 15]

#### Data is Key for Future Workloads

Chrome

Google's web browser

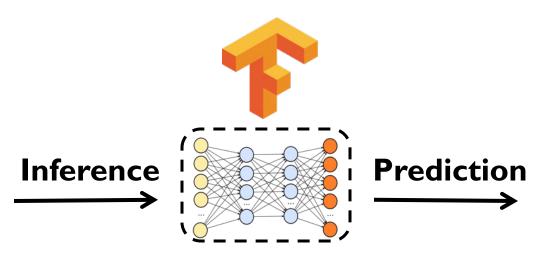

#### **TensorFlow Mobile**

Google's machine learning framework

Google's video codec

Google's video codec

#### Data Overwhelms Modern Machines

**TensorFlow Mobile**

Data → performance & energy bottleneck

VP9

VouTube

Video Playback

Google's video codec

Google's video codec

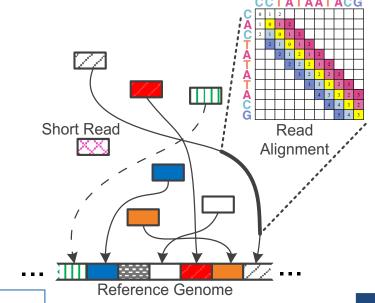

## Data is Key for Future Workloads

Sequencing

**Genome Analysis**

Read Mapping

## Data → performance & energy bottleneck

read4: CGCTTCCAT

read5: CCATGACGC read6: TTCCATGAC

**Scientific Discovery**

Variant Calling

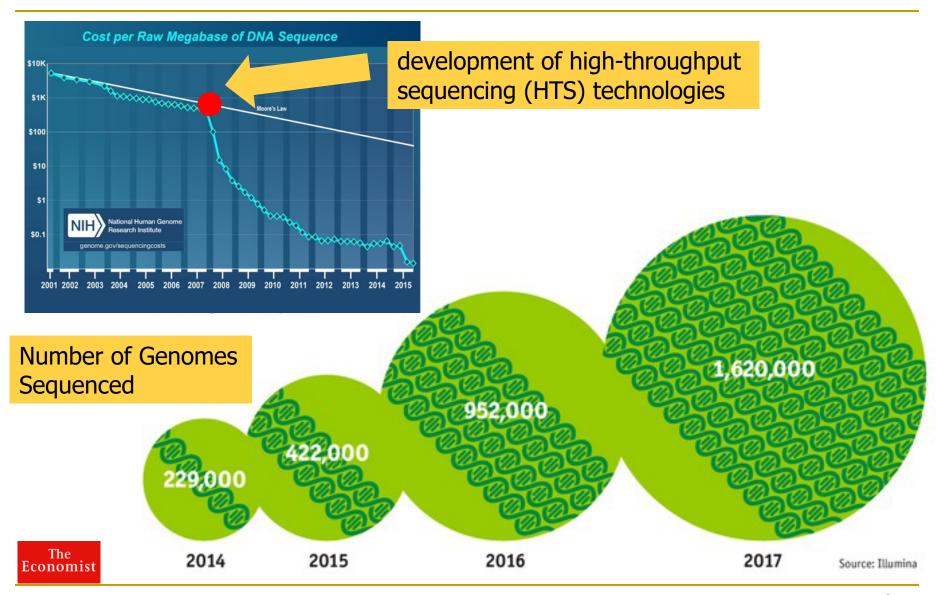

## We Need Faster & Scalable Genome Analysis

Understanding **genetic variations**, **species**, **evolution**, ...

Rapid surveillance of **disease outbreaks**

Predicting the presence and relative abundance of **microbes** in a sample

Developing personalized medicine

## New Genome Sequencing Technologies

## Nanopore sequencing technology and tools for genome assembly: computational analysis of the current state, bottlenecks and future directions

Damla Senol Cali ™, Jeremie S Kim, Saugata Ghose, Can Alkan, Onur Mutlu

Briefings in Bioinformatics, bby017, https://doi.org/10.1093/bib/bby017

Published: 02 April 2018 Article history ▼

Oxford Nanopore MinION

Senol Cali+, "Nanopore Sequencing Technology and Tools for Genome Assembly: Computational Analysis of the Current State, Bottlenecks and Future Directions," Briefings in Bioinformatics, 2018.

[Open arxiv.org version]

## New Genome Sequencing Technologies

## Nanopore sequencing technology and tools for genome assembly: computational analysis of the current state, bottlenecks and future directions

Damla Senol Cali ™, Jeremie S Kim, Saugata Ghose, Can Alkan, Onur Mutlu

Briefings in Bioinformatics, bby017, https://doi.org/10.1093/bib/bby017

Published: 02 April 2018 Article history ▼

Oxford Nanopore MinION

## Data → performance & energy bottleneck

## Problems with (Genome) Analysis Today

**Special-Purpose** Machine for **Data Generation**

General-Purpose Machine for Data Analysis

FAST

**SLOW**

Slow and inefficient processing capability Large amounts of data movement

## Accelerating Genome Analysis [DAC 2023]

Onur Mutlu and Can Firtina,

"Accelerating Genome Analysis via Algorithm-Architecture Co-Design"

Invited Special Session Paper in Proceedings of the 60th Design Automation Conference (**DAC**), San Francisco, CA, USA, July 2023. [arXiv version]

## Accelerating Genome Analysis via Algorithm-Architecture Co-Design

Onur Mutlu Can Firtina

ETH Zürich

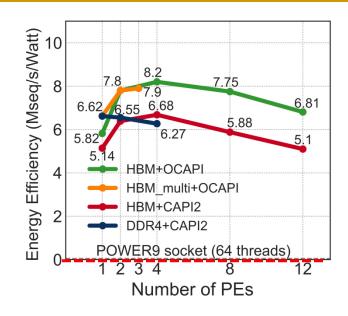

## Accelerating Genome Analysis [IEEE MICRO 2020]

Mohammed Alser, Zulal Bingol, Damla Senol Cali, Jeremie Kim, Saugata Ghose, Can Alkan, and Onur Mutlu,

"Accelerating Genome Analysis: A Primer on an Ongoing Journey"

IEEE Micro (IEEE MICRO), Vol. 40, No. 5, pages 65-75, September/October 2020.

[Slides (pptx)(pdf)]

[Talk Video (1 hour 2 minutes)]

# Accelerating Genome Analysis: A Primer on an Ongoing Journey

#### **Mohammed Alser**

ETH Zürich

#### Zülal Bingöl

Bilkent University

#### Damla Senol Cali

Carnegie Mellon University

#### Jeremie Kim

ETH Zurich and Carnegie Mellon University

#### **Saugata Ghose**

University of Illinois at Urbana–Champaign and Carnegie Mellon University

#### Can Alkan

Bilkent University

#### **Onur Mutlu**

ETH Zurich, Carnegie Mellon University, and Bilkent University

## Beginner Reading on Genome Analysis

Mohammed Alser, Joel Lindegger, Can Firtina, Nour Almadhoun, Haiyu Mao, Gagandeep Singh, Juan Gomez-Luna, Onur Mutlu

"From Molecules to Genomic Variations to Scientific Discovery:

Intelligent Algorithms and Architectures for Intelligent Genome Analysis"

Computational and Structural Biotechnology Journal, 2022

Source code

journal homepage: www.elsevier.com/locate/csbj

#### Review

From molecules to genomic variations: Accelerating genome analysis via intelligent algorithms and architectures

Mohammed Alser\*, Joel Lindegger, Can Firtina, Nour Almadhoun, Haiyu Mao, Gagandeep Singh, Juan Gomez-Luna, Onur Mutlu\*

ETH Zurich, Gloriastrasse 35, 8092 Zürich, Switzerland

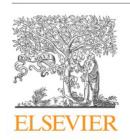

## FPGA-based Near-Memory Analytics

Gagandeep Singh, Mohammed Alser, Damla Senol Cali, Dionysios

Diamantopoulos, Juan Gómez-Luna, Henk Corporaal, and Onur Mutlu,

"FPGA-based Near-Memory Acceleration of Modern Data-Intensive

Applications"

IFFE Micro (IEEE MICRO), 2021.

## FPGA-based Near-Memory Acceleration of Modern Data-Intensive Applications

Gagandeep Singh<sup>⋄</sup> Mohammed Alser<sup>⋄</sup> Damla Senol Cali<sup>⋈</sup>

Dionysios Diamantopoulos<sup>▽</sup> Juan Gómez-Luna<sup>⋄</sup>

Henk Corporaal<sup>⋆</sup> Onur Mutlu<sup>⋄⋈</sup>

<sup>⋄</sup>ETH Zürich <sup>⋈</sup> Carnegie Mellon University \*Eindhoven University of Technology <sup>▽</sup>IBM Research Europe

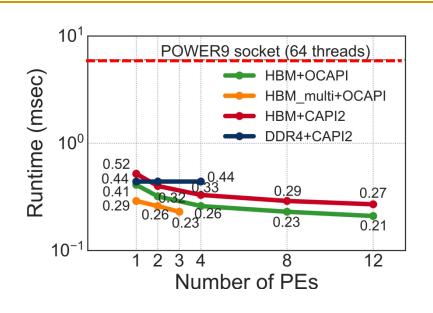

### Near-Memory Acceleration using FPGAs

#### **Near-HBM FPGA-based accelerator**

Two communication technologies: CAPI2 and OCAPI

Two memory technologies: DDR4 and HBM

Two workloads: Weather Modeling and Genome Analysis

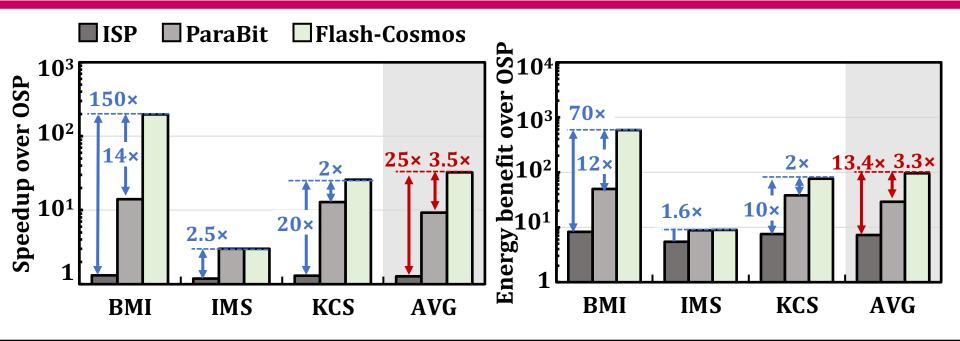

### Performance & Energy Greatly Improve

5-27× performance vs. a 16-core (64-thread) IBM POWER9 CPU

12-133× energy efficiency vs. a 16-core (64-thread) IBM POWER9 CPU

**HBM alleviates memory bandwidth contention vs. DDR4**

#### GenASM Framework [MICRO 2020]

Damla Senol Cali, Gurpreet S. Kalsi, Zulal Bingol, Can Firtina, Lavanya Subramanian, Jeremie S. Kim, Rachata Ausavarungnirun, Mohammed Alser, Juan Gomez-Luna, Amirali Boroumand, Anant Nori, Allison Scibisz, Sreenivas Subramoney, Can Alkan, Saugata Ghose, and Onur Mutlu, "GenASM: A High-Performance, Low-Power Approximate String Matching Acceleration Framework for Genome Sequence Analysis"

Proceedings of the <u>53rd International Symposium on Microarchitecture</u> (MICRO), Virtual, October 2020.

[<u>Lighting Talk Video</u> (1.5 minutes)]

[<u>Lightning Talk Slides (pptx) (pdf)</u>]

[<u>Talk Video</u> (18 minutes)]

[<u>Slides (pptx) (pdf)</u>]

#### GenASM: A High-Performance, Low-Power Approximate String Matching Acceleration Framework for Genome Sequence Analysis

Damla Senol Cali<sup>†™</sup> Gurpreet S. Kalsi<sup>™</sup> Zülal Bingöl<sup>▽</sup> Can Firtina<sup>⋄</sup> Lavanya Subramanian<sup>‡</sup> Jeremie S. Kim<sup>⋄†</sup> Rachata Ausavarungnirun<sup>⊙</sup> Mohammed Alser<sup>⋄</sup> Juan Gomez-Luna<sup>⋄</sup> Amirali Boroumand<sup>†</sup> Anant Nori<sup>™</sup> Allison Scibisz<sup>†</sup> Sreenivas Subramoney<sup>™</sup> Can Alkan<sup>▽</sup> Saugata Ghose<sup>\*†</sup> Onur Mutlu<sup>⋄†▽</sup>

† Carnegie Mellon University <sup>™</sup> Processor Architecture Research Lab, Intel Labs <sup>▽</sup> Bilkent University <sup>⋄</sup> ETH Zürich

‡ Facebook <sup>⊙</sup> King Mongkut's University of Technology North Bangkok <sup>\*</sup> University of Illinois at Urbana–Champaign

21

## Scrooge: Overcoming GenASM Limitations

Joël Lindegger, Damla Senol Cali, Mohammed Alser, Juan Gómez-Luna, Nika Mansouri Ghiasi, and Onur Mutlu,

<u>"Scrooge: A Fast and Memory-Frugal Genomic Sequence Aligner for CPUs, GPUs, and ASICs"</u>

**Bioinformatics**, [published online on] 24 March 2023.

Online link at Bioinformatics Journal

[arXiv preprint]

[Scrooge Source Code]

## Scrooge: A Fast and Memory-Frugal Genomic Sequence Aligner for CPUs, GPUs, and ASICs

Joël Lindegger<sup>§</sup> Juan Gómez-Luna<sup>§</sup> Damla Senol Cali<sup>†</sup> Nika Mansouri Ghiasi<sup>§</sup> Mohammed Alser§

Onur Mutlu§

§ETH Zürich

†Bionano Genomics

## In-Storage Genome Filtering [ASPLOS 2022]

Nika Mansouri Ghiasi, Jisung Park, Harun Mustafa, Jeremie Kim, Ataberk Olgun, Arvid Gollwitzer, Damla Senol Cali, Can Firtina, Haiyu Mao, Nour Almadhoun Alserr, Rachata Ausavarungnirun, Nandita Vijaykumar, Mohammed Alser, and Onur Mutlu, "GenStore: A High-Performance and Energy-Efficient In-Storage Computing System for Genome Sequence Analysis"

Proceedings of the <u>27th International Conference on Architectural Support for</u>

<u>Programming Languages and Operating Systems</u> (**ASPLOS**), Virtual, February-March 2022.

[Talk Slides (pptx) (pdf)]

[Lightning Talk Slides (pptx) (pdf)]

[Lightning Talk Video (90 seconds)]

[Talk Video (17 minutes)]

## GenStore: A High-Performance In-Storage Processing System for Genome Sequence Analysis

Nika Mansouri Ghiasi¹ Jisung Park¹ Harun Mustafa¹ Jeremie Kim¹ Ataberk Olgun¹ Arvid Gollwitzer¹ Damla Senol Cali² Can Firtina¹ Haiyu Mao¹ Nour Almadhoun Alserr¹ Rachata Ausavarungnirun³ Nandita Vijaykumar⁴ Mohammed Alser¹ Onur Mutlu¹

<sup>1</sup>ETH Zürich <sup>2</sup>Bionano Genomics <sup>3</sup>KMUTNB <sup>4</sup>University of Toronto

## Accelerating Sequence-to-Graph Mapping

Damla Senol Cali, Konstantinos Kanellopoulos, Joel Lindegger, Zulal Bingol, Gurpreet S. Kalsi, Ziyi Zuo, Can Firtina, Meryem Banu Cavlak, Jeremie Kim, Nika MansouriGhiasi, Gagandeep Singh, Juan Gomez-Luna, Nour Almadhoun Alserr, Mohammed Alser, Sreenivas Subramoney, Can Alkan, Saugata Ghose, and Onur Mutlu, "SeGraM: A Universal Hardware Accelerator for Genomic Sequence-to-Graph and Sequence-to-Sequence Mapping"

Proceedings of the <u>49th International Symposium on Computer Architecture</u> (**ISCA**), New York, June 2022.

arXiv version

## SeGraM: A Universal Hardware Accelerator for Genomic Sequence-to-Graph and Sequence-to-Sequence Mapping

Damla Senol Cali<sup>1</sup> Konstantinos Kanellopoulos<sup>2</sup> Joël Lindegger<sup>2</sup> Zülal Bingöl<sup>3</sup> Gurpreet S. Kalsi<sup>4</sup> Ziyi Zuo<sup>5</sup> Can Firtina<sup>2</sup> Meryem Banu Cavlak<sup>2</sup> Jeremie Kim<sup>2</sup> Nika Mansouri Ghiasi<sup>2</sup> Gagandeep Singh<sup>2</sup> Juan Gómez-Luna<sup>2</sup> Nour Almadhoun Alserr<sup>2</sup> Mohammed Alser<sup>2</sup> Sreenivas Subramoney<sup>4</sup> Can Alkan<sup>3</sup> Saugata Ghose<sup>6</sup> Onur Mutlu<sup>2</sup>

<sup>1</sup>Bionano Genomics <sup>2</sup>ETH Zürich <sup>3</sup>Bilkent University <sup>4</sup>Intel Labs <sup>5</sup>Carnegie Mellon University <sup>6</sup>University of Illinois Urbana-Champaign

## Accelerating Basecalling + Read Mapping

Haiyu Mao, Mohammed Alser, Mohammad Sadrosadati, Can Firtina, Akanksha Baranwal, Damla Senol Cali, Aditya Manglik, Nour Almadhoun Alserr, and Onur Mutlu,

"GenPIP: In-Memory Acceleration of Genome Analysis via Tight Integration of Basecalling and Read Mapping"

Proceedings of the <u>55th International Symposium on Microarchitecture</u> (**MICRO**), Chicago, IL, USA, October 2022.

[Slides (pptx) (pdf)]

[Longer Lecture Slides (pptx) (pdf)]

[<u>Lecture Video</u> (25 minutes)]

[arXiv version]

## GenPIP: In-Memory Acceleration of Genome Analysis via Tight Integration of Basecalling and Read Mapping

Haiyu Mao<sup>1</sup> Mohammed Alser<sup>1</sup> Mohammad Sadrosadati<sup>1</sup> Can Firtina<sup>1</sup> Akanksha Baranwal<sup>1</sup>

Damla Senol Cali<sup>2</sup> Aditya Manglik<sup>1</sup> Nour Almadhoun Alserr<sup>1</sup> Onur Mutlu<sup>1</sup>

\*\*Prescription\*\* \*\*Propries\*\*: Propries\*\*: Akanksha Baranwal<sup>1</sup>

\*\*Prescription\*\* \*\*Propries\*\*: Akanksha Baranwal<sup>1</sup>

\*\*Prescription\*\* \*\*Prescription\*\*: Akanksha Baranwal<sup>1</sup>

\*\*Prescription\*\*: Prescription\*\*: Akanksha Baranwal<sup>1</sup>

\*\*Prescription\*\*: Akanksha Baranwal<sup>1</sup>

\*\*Prescripti

## Designing & Accelerating Basecallers

#### A Framework for Designing Efficient Deep Learning-Based Genomic Basecallers

Gagandeep Singh $^a$  Mohammed Alser $^{*a}$  Alireza Khodamoradi $^{*b}$  Kristof Denolf $^b$  Can Firtina $^a$  Meryem Banu Cavlak $^a$  Henk Corporaal $^c$  Onur Mutlu $^a$   $^a$ ETH Zürich  $^b$ AMD  $^c$ Eindhoven University of Technology

Nanopore sequencing is a widely-used high-throughput genome sequencing technology that can sequence long fragments of a genome. Nanopore sequencing generates noisy electrical signals that need to be converted into a standard string of DNA nucleotide bases (i.e., A, C, G, T) using a computational step called *basecalling*. The accuracy and speed of basecalling have critical implications for every subsequent step in genome analysis. Currently, basecallers are developed mainly based on deep learning techniques to provide high sequencing accuracy without considering the compute demands of such tools. We observe that state-of-the-art basecallers (i.e., Guppy, Bonito, Fast-Bonito) are slow, inefficient, and memory-hungry

## Future of Genome Sequencing & Analysis

Mohammed Alser, Zülal Bingöl, Damla Senol Cali, Jeremie Kim, Saugata Ghose, Can Alkan, Onur Mutlu "Accelerating Genome Analysis: A Primer on an Ongoing Journey" IEEE Micro, August 2020.

## More on Fast & Efficient Genome Analysis ...

Onur Mutlu,

"Accelerating Genome Analysis: A Primer on an Ongoing Journey"

*Invited Lecture at <u>Technion</u>*, Virtual, 26 January 2021.

[Slides (pptx) (pdf)]

[Talk Video (1 hour 37 minutes, including Q&A)]

[Related Invited Paper (at IEEE Micro, 2020)]

## More on Fast & Efficient Genome Analysis ...

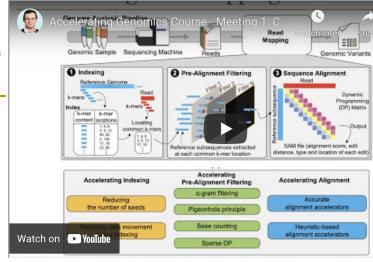

## Detailed Lectures on Genome Analysis

- Computer Architecture, Fall 2020, Lecture 3a

- Introduction to Genome Sequence Analysis (ETH Zürich, Fall 2020)

- https://www.youtube.com/watch?v=CrRb32v7SJc&list=PL5Q2soXY2Zi9xidyIgBxUz7xRPS-wisBN&index=5

- Computer Architecture, Fall 2020, Lecture 8

- Intelligent Genome Analysis (ETH Zürich, Fall 2020)

- https://www.youtube.com/watch?v=ygmQpdDTL7o&list=PL5Q2soXY2Zi9xidyIgBxUz7xRPS-wisBN&index=14

- Computer Architecture, Fall 2020, Lecture 9a

- GenASM: Approx. String Matching Accelerator (ETH Zürich, Fall 2020)

- https://www.youtube.com/watch?v=XoLpzmN Pas&list=PL5Q2soXY2Zi9xidyIgBxUz7xRPS-wisBN&index=15

- Accelerating Genomics Project Course, Fall 2020, Lecture 1

- Accelerating Genomics (ETH Zürich, Fall 2020)

- https://www.youtube.com/watch?v=rgjl8ZyLsAg&list=PL5Q2soXY2Zi9E2bBVAgCqL gwiDRQDTyId

#### Genomics Course (Fall 2022)

#### Fall 2022 Edition:

https://safari.ethz.ch/projects and seminars/fall2022/do ku.php?id=bioinformatics

#### Spring 2022 Edition:

https://safari.ethz.ch/projects and seminars/spring2022/doku.php?id=bioinformatics

#### Youtube Livestream (Fall 2022):

https://www.youtube.com/watch?v=nA41964-9r8&list=PL5Q2soXY2Zi8tFlQvdxOdizD\_EhVAMVQV

#### Youtube Livestream (Spring 2022):

https://www.youtube.com/watch?v=DEL\_5A\_Y3TI&list= PL5Q2soXY2Zi8NrPDgOR1yRU\_Cxxjw-u18

#### Project course

- Taken by Bachelor's/Master's students

- Genomics lectures

- Hands-on research exploration

- Many research readings

https://www.youtube.com/onurmutlulectures

#### Spring 2022 Meetings/Schedule

| Week | Date          | Livestream        | Meeting                                                                           | Learning<br>Materials                             |

|------|---------------|-------------------|-----------------------------------------------------------------------------------|---------------------------------------------------|

| W1   | 11.3<br>Fri.  | You to Live       | M1: P&S Accelerating Genomics Course Introduction & Project Proposals (PDF) (PPT) | Required<br>Materials<br>Recommended<br>Materials |

| W2   | 18.3<br>Fri.  | You Tube Live     | M2: Introduction to Sequencing (PDF) (PPT)                                        |                                                   |

| W3   | 25.3<br>Fri.  | You Tube Premiere | M3: Read Mapping  (PDF) (PPT)                                                     |                                                   |

| W4   | 01.04<br>Fri. | You Tube Premiere | M4: GateKeeper  (PDF) (PPT)                                                       |                                                   |

| W5   | 08.04<br>Fri. | You Tube Premiere | M5: MAGNET & Shouji  (PDF) (PPT)                                                  |                                                   |

| W6   | 15.4<br>Fri.  | You Tube Premiere | M6: SneakySnake  (PDF) (PPT)                                                      |                                                   |

| W7   | 29.4<br>Fri.  | You Tube Premiere | M7: GenStore  (PDF) (PPT)                                                         |                                                   |

| W8   | 06.05<br>Fri. | You Tube Premiere | M8: GRIM-Filter  (PDF) (PPT)                                                      |                                                   |

| W9   | 13.05<br>Fri. | You Tube Premiere | M9: Genome Assembly  (PDF) (PPT)                                                  |                                                   |

| W10  | 20.05<br>Fri. | You Tube Live     | M10: Genomic Data Sharing Under Differential Privacy (PDF) (PPT)                  |                                                   |

| W11  | 10.06<br>Fri. | You Tube Premiere | M11: Accelerating Genome<br>Sequence Analysis<br>(PDF) (PPT)                      |                                                   |

## BIO-Arch Workshop at RECOMB 2023

#### April 14, 2023

#### BIO-Arch: Workshop on Hardware Acceleration of Bioinformatics Workloads

#### **About**

BIO-Arch is a new forum for presenting and discussing new ideas in accelerating bioinformatics workloads with the co-design of hardware & software and the use of new computer architectures. Our goal is to discuss new system designs tailored for bioinformatics. BIO-Arch aims to bring together researchers in the bioinformatics, computational biology, and computer architecture communities to strengthen the progress in accelerating bioinformatics analysis (e.g., genome analysis) with efficient system designs that include hardware acceleration and software systems tailored fo new hardware technologies.

#### Venue

BIO-Arch will be held in The Social Facilities of İstanbul Technical University on **April 14**. Detailed information about how to arrive at the venue location with various transportation options can be found on the RECOMB website.

Our panel discussion will be held in conjunction with the main RECOMB conference. The panel discussion will be held in Marriott Şişli on **April 17 at 17:00**. You can find

https://www.youtube.com/watch?v=2rCsb4-nLmg

#### Data Overwhelms Modern Machines ...

Storage/memory capability

Communication capability

Computation capability

Greatly impacts robustness, energy, performance, cost

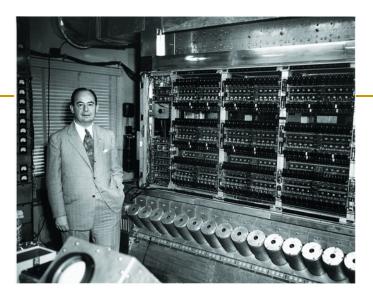

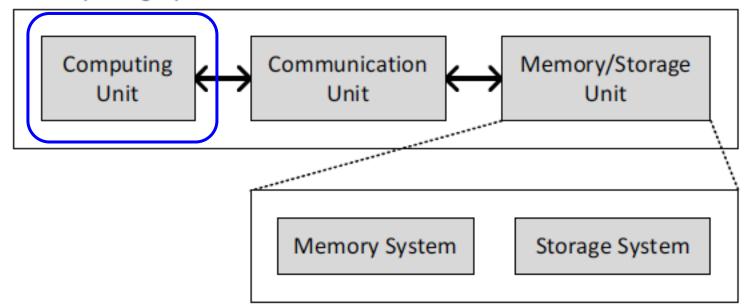

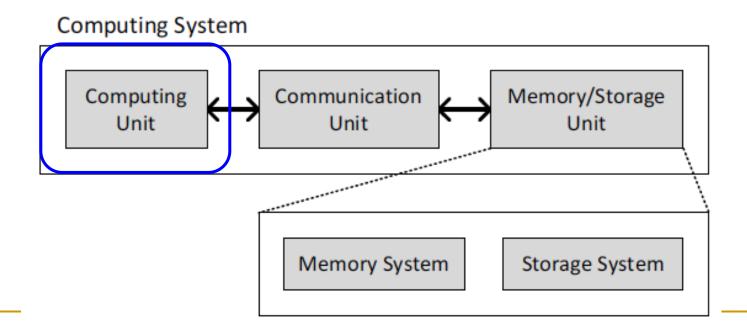

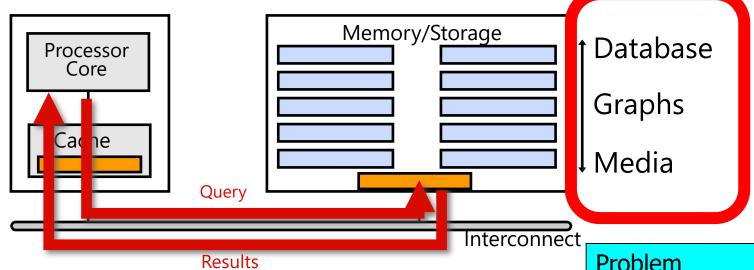

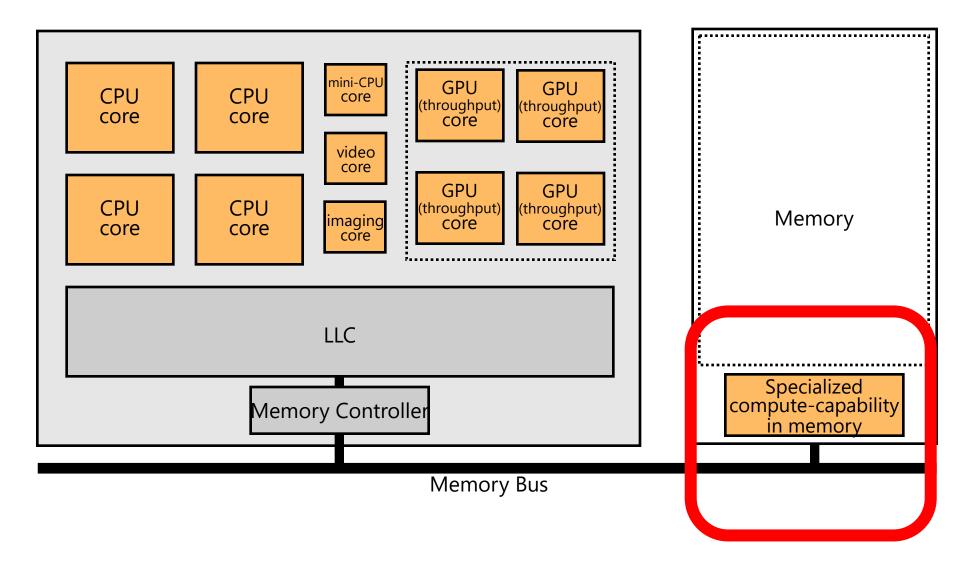

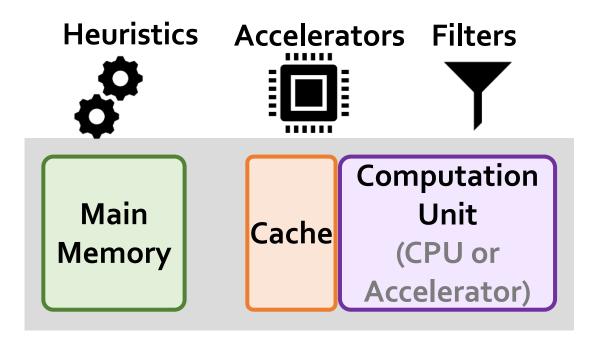

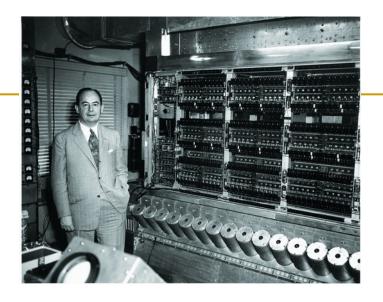

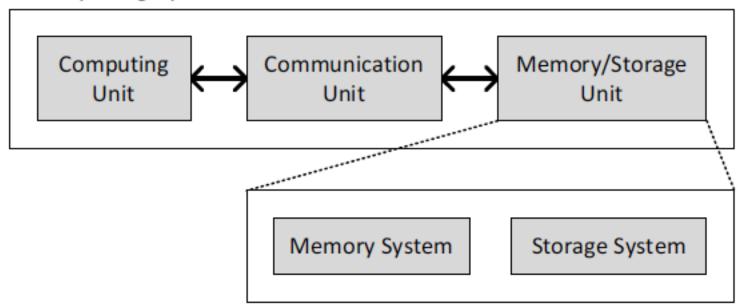

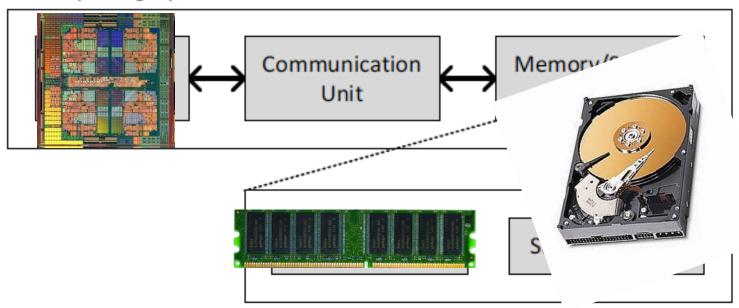

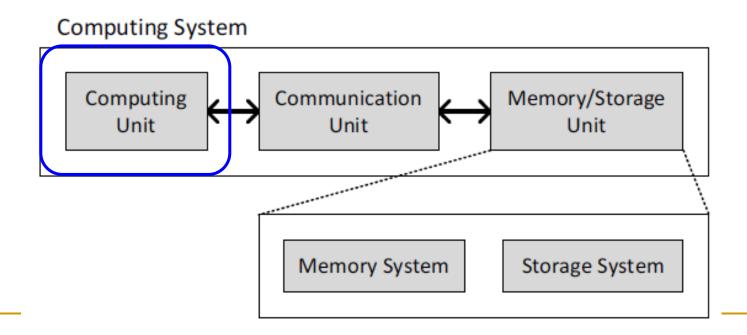

## A Computing System

- Three key components

- Computation

- Communication

- Storage/memory

Burks, Goldstein, von Neumann, "Preliminary discussion of the logical design of an electronic computing instrument," 1946.

#### **Computing System**

34

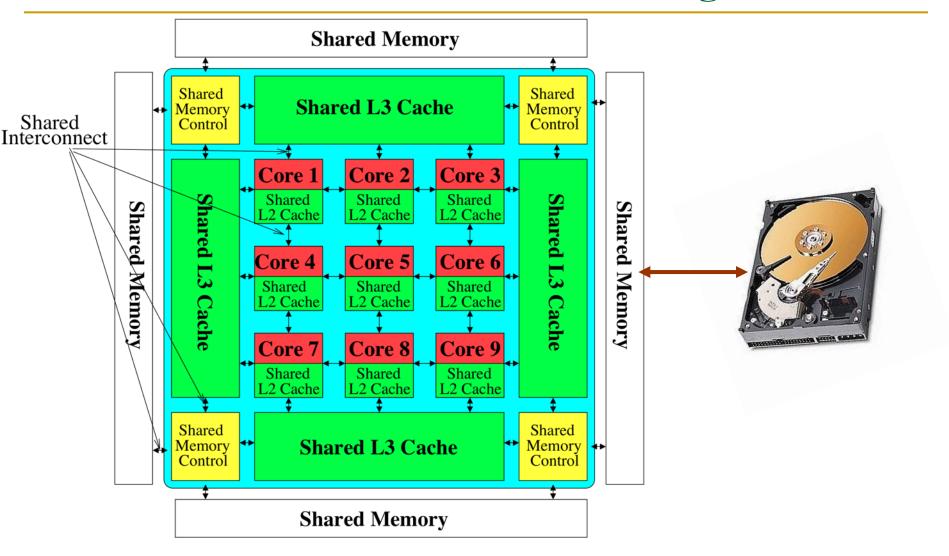

## Perils of Processor-Centric Design

Most of the system is dedicated to storing and moving data

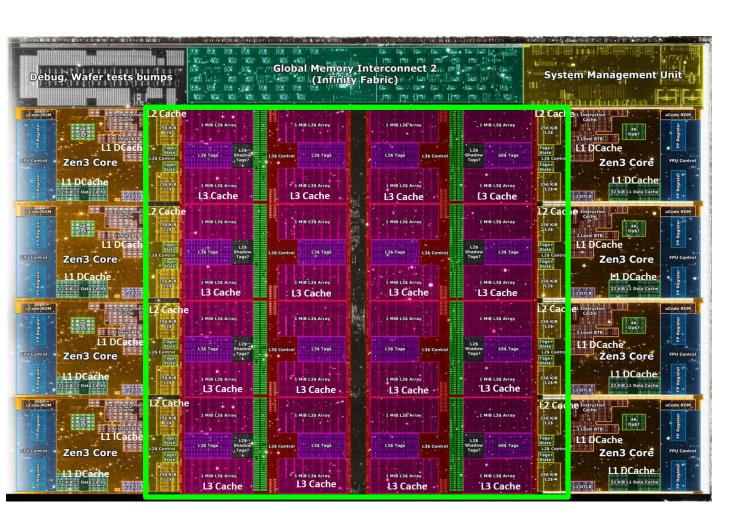

## Deeper and Larger Memory Hierarchies

**Core Count:**

8 cores/16 threads

L1 Caches:

32 KB per core

L2 Caches:

512 KB per core

L3 Cache:

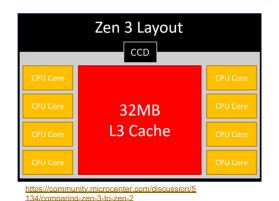

32 MB shared

AMD Ryzen 5000, 2020

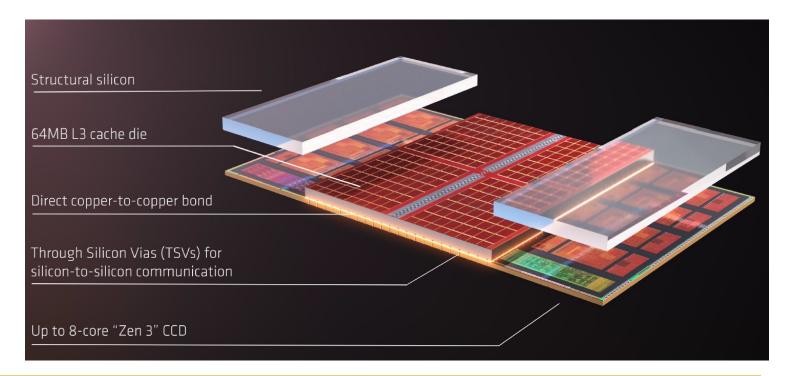

## AMD's 3D Last Level Cache (2021)

AMD increases the L3 size of their 8-core Zen 3 processors from 32 MB to 96 MB

Additional 64 MB L3 cache die stacked on top of the processor die

- Connected using Through Silicon Vias (TSVs)

- Total of 96 MB L3 cache

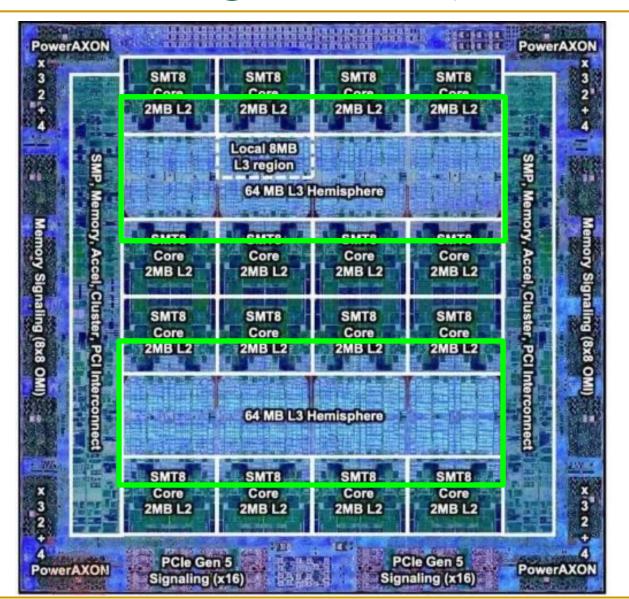

## Deeper and Larger Memory Hierarchies

IBM POWER10, 2020

#### Cores:

15-16 cores, 8 threads/core

L2 Caches:

2 MB per core

L3 Cache:

120 MB shared

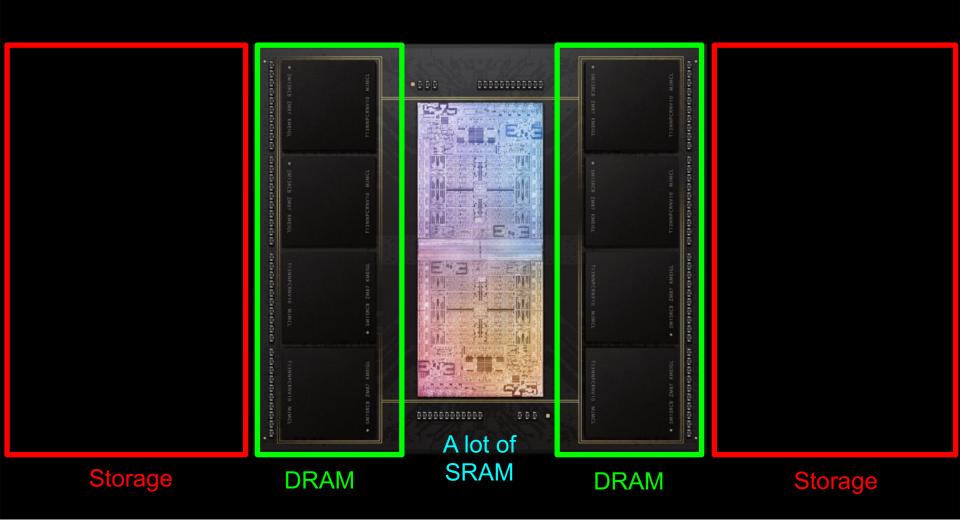

## Deeper and Larger Memory Hierarchies

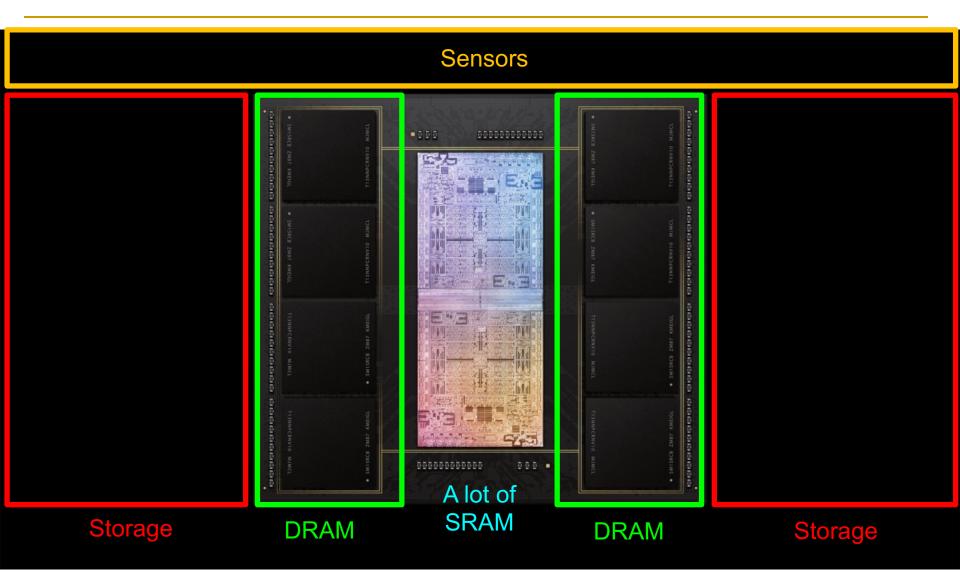

Apple M1 Ultra System (2022)

#### Data Overwhelms Modern Machines

**TensorFlow Mobile**

## Data → performance & energy bottleneck

VP9

VouTube

Video Playback

Google's video codec

Google's video codec

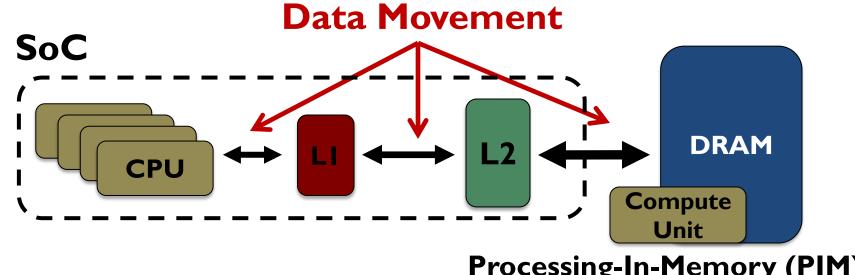

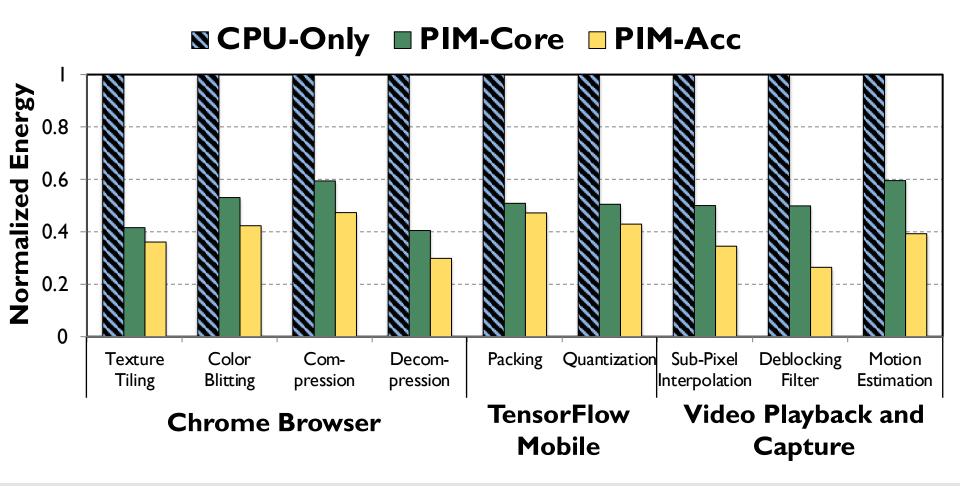

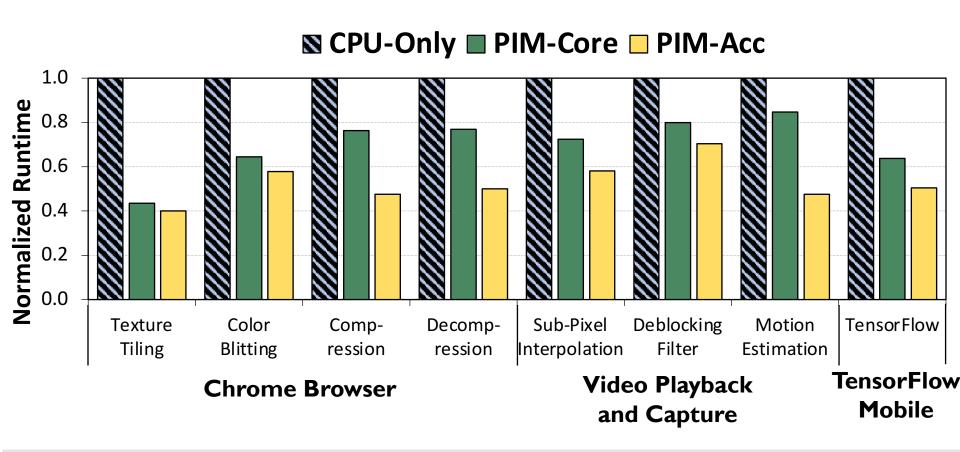

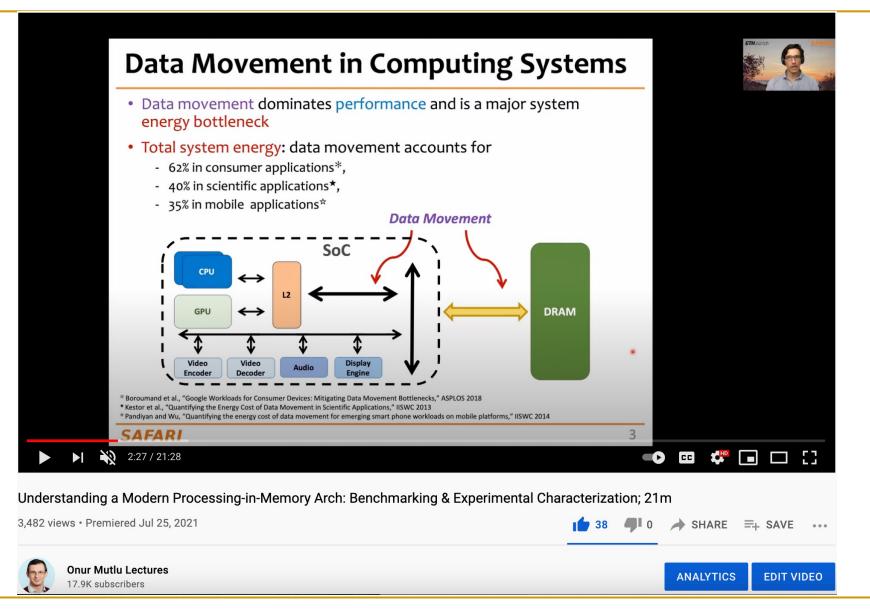

#### Data Movement Overwhelms Modern Machines

Amirali Boroumand, Saugata Ghose, Youngsok Kim, Rachata Ausavarungnirun, Eric Shiu, Rahul Thakur, Daehyun Kim, Aki Kuusela, Allan Knies, Parthasarathy Ranganathan, and Onur Mutlu, "Google Workloads for Consumer Devices: Mitigating Data Movement Bottlenecks" Proceedings of the <u>23rd International Conference on Architectural Support for Programming</u> <u>Languages and Operating Systems</u> (ASPLOS), Williamsburg, VA, USA, March 2018.

## 62.7% of the total system energy is spent on data movement

## Google Workloads for Consumer Devices: Mitigating Data Movement Bottlenecks

Amirali Boroumand<sup>1</sup> Rachata Ausavarungnirun<sup>1</sup> Aki Kuusela<sup>3</sup> Allan Knies<sup>3</sup>

Saugata Ghose<sup>1</sup> Youngsok Kim<sup>2</sup>

Eric Shiu<sup>3</sup> Rahul Thakur<sup>3</sup> Daehyun Kim<sup>4,3</sup>

Parthasarathy Ranganathan<sup>3</sup> Onur Mutlu<sup>5,1</sup>

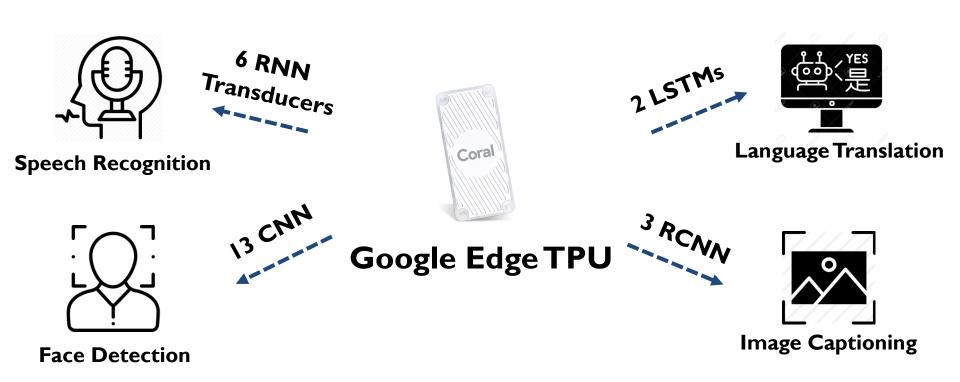

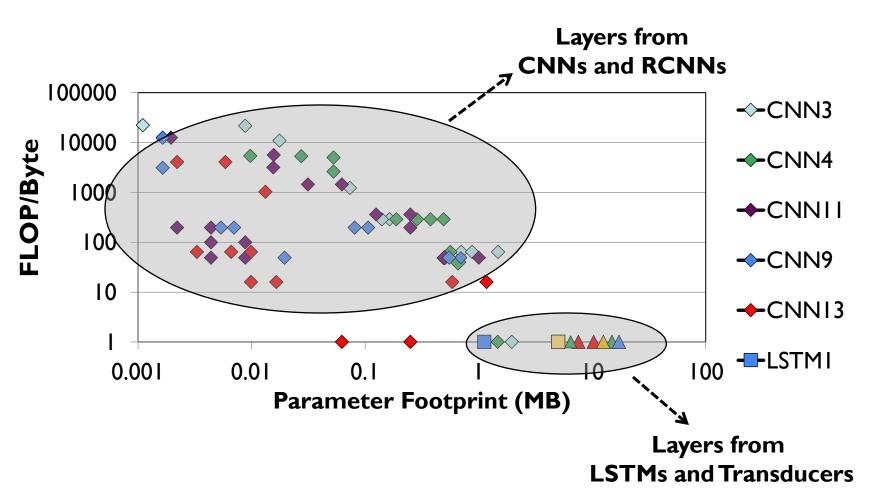

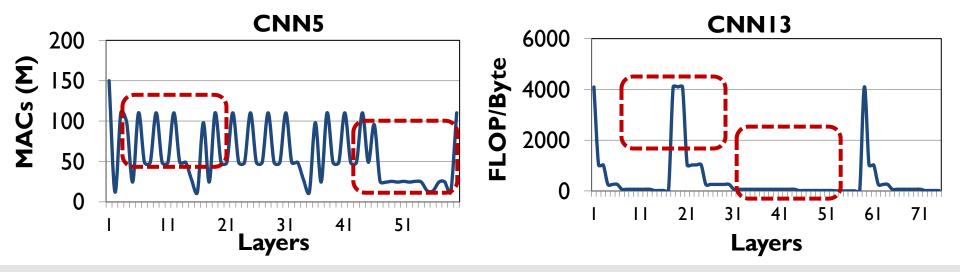

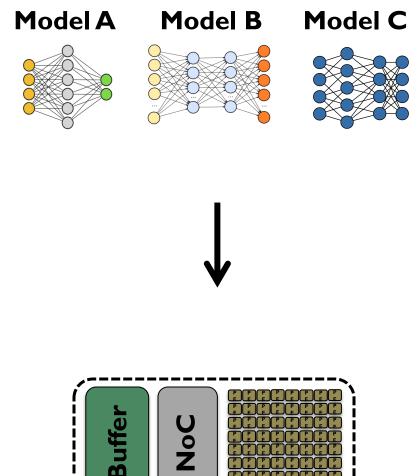

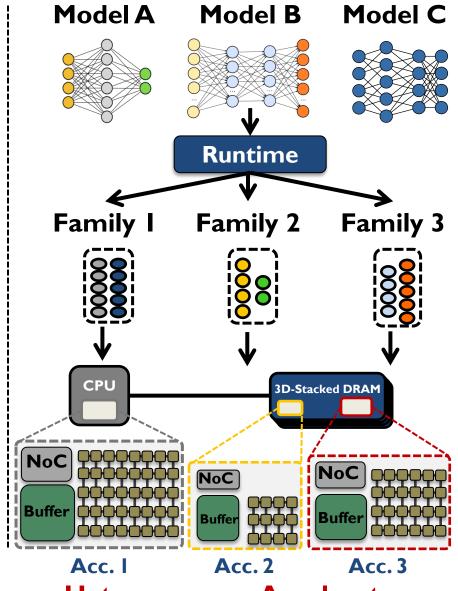

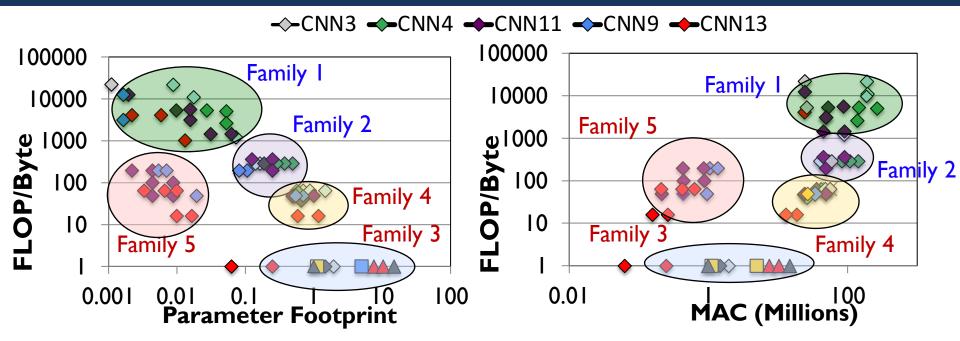

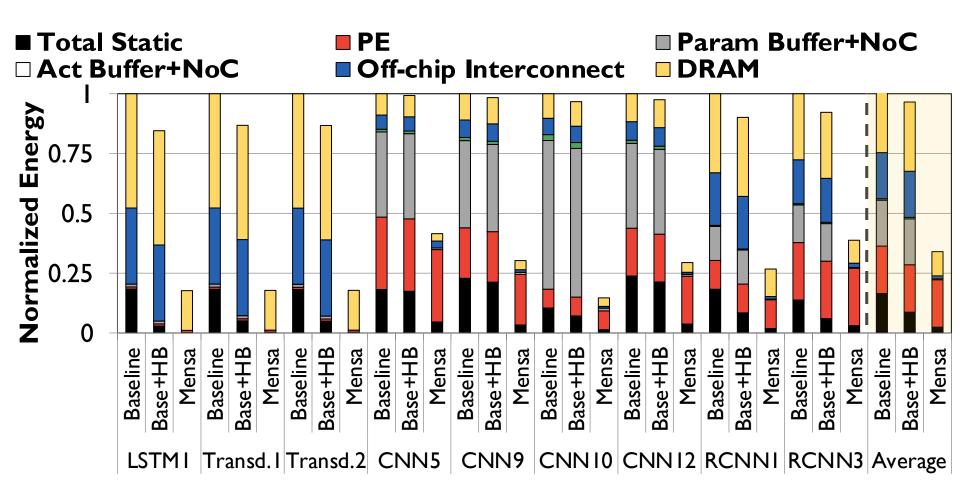

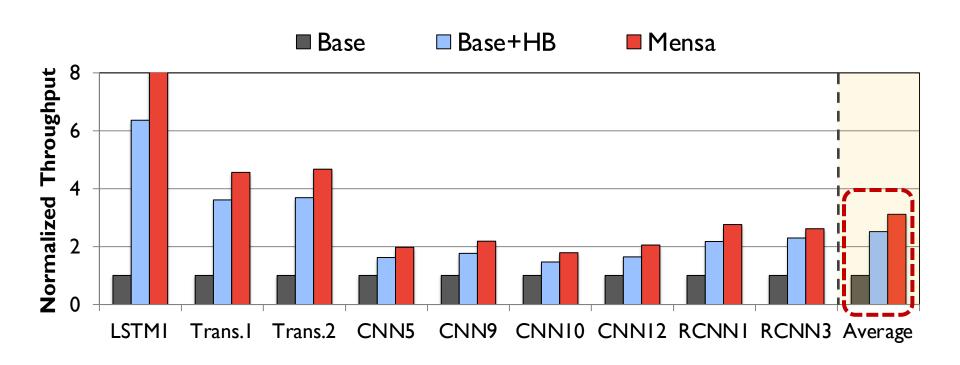

#### Data Movement Overwhelms Accelerators

Amirali Boroumand, Saugata Ghose, Berkin Akin, Ravi Narayanaswami, Geraldo F. Oliveira,

Xiaoyu Ma, Eric Shiu, and Onur Mutlu,

"Google Neural Network Models for Edge Devices: Analyzing and Mitigating Machine Learning Inference Bottlenecks"

Proceedings of the <u>30th International Conference on Parallel Architectures and Compilation</u> <u>Techniques</u> (**PACT**), Virtual, September 2021.

[Slides (pptx) (pdf)]

[Talk Video (14 minutes)]

## > 90% of the total system energy is spent on memory in large ML models

#### Google Neural Network Models for Edge Devices: Analyzing and Mitigating Machine Learning Inference Bottlenecks

Amirali Boroumand<sup>†</sup>

Saugata Ghose<sup>‡</sup>

Berkin Akin<sup>§</sup>

Ravi Narayanaswami<sup>§</sup>

Geraldo F. Oliveira<sup>⋆</sup>

Xiaoyu Ma<sup>§</sup>

Eric Shiu<sup>§</sup>

Onur Mutlu<sup>⋆†</sup>

†Carnegie Mellon Univ.

Stanford Univ.

Univ. of Illinois Urbana-Champaign

Google

ETH Zürich

CAFADI

## An Intelligent Architecture Handles Data Well

#### How to Handle Data Well

- Ensure data does not overwhelm the components

- via intelligent algorithms, architectures & system designs: algorithm-architecture-devices

- Take advantage of vast amounts of data and metadata

- to improve architectural & system-level decisions

- Understand and exploit properties of (different) data

- to improve algorithms & architectures in various metrics

## Corollaries: Computing Systems Today ...

Are processor-centric vs. data-centric

Make designer-dictated decisions vs. data-driven

Make component-based myopic decisions vs. data-aware

## Fundamentally Better Architectures

## **Data-centric**

**Data-driven**

**Data-aware**

#### We Need to Revisit the Entire Stack

We can get there step by step

### A Blueprint for Fundamentally Better Architectures

Onur Mutlu,

"Intelligent Architectures for Intelligent Computing Systems"

Invited Paper in Proceedings of the <u>Design, Automation, and Test in</u> <u>Europe Conference</u> (**DATE**), Virtual, February 2021.

[Slides (pptx) (pdf)]

[IEDM Tutorial Slides (pptx) (pdf)]

[Short DATE Talk Video (11 minutes)]

[Longer IEDM Tutorial Video (1 hr 51 minutes)]

#### Intelligent Architectures for Intelligent Computing Systems

Onur Mutlu ETH Zurich omutlu@gmail.com

48

## Data-Centric (Memory-Centric) Architectures

## Data-Centric Architectures: Properties

- Process data where it resides (where it makes sense)

- Processing in and near memory & sensor structures

Low-latency & low-energy data access

- Low-cost data storage & processing

- High capacity memory at low cost: hybrid memory, compression

- Intelligent data management

- Intelligent controllers handling robustness, security, cost, perf.

## Processing Data Where It Makes Sense

#### Process Data Where It Makes Sense

Apple M1 Ultra System (2022)

## Processing in/near Memory: An Old Idea

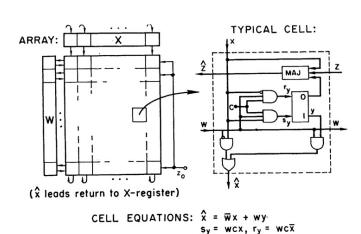

Kautz, "Cellular Logic-in-Memory Arrays", IEEE TC 1969.

IEEE TRANSACTIONS ON COMPUTERS, VOL. C-18, NO. 8, AUGUST 1969

#### Cellular Logic-in-Memory Arrays

WILLIAM H. KAUTZ, MEMBER, IEEE

Abstract—As a direct consequence of large-scale integration, many advantages in the design, fabrication, testing, and use of digital circuitry can be achieved if the circuits can be arranged in a two-dimensional iterative, or cellular, array of identical elementary networks, or cells. When a small amount of storage is included in each cell, the same array may be regarded either as a logically enhanced memory array, or as a logic array whose elementary gates and connections can be "programmed" to realize a desired logical behavior.

In this paper the specific engineering features of such cellular logic-in-memory (CLIM) arrays are discussed, and one such special-purpose array, a cellular sorting array, is described in detail to illustrate how these features may be achieved in a particular design. It is shown how the cellular sorting array can be employed as a single-address, multiword memory that keeps in order all words stored within it. It can also be used as a content-addressed memory, a pushdown memory, a buffer memory, and (with a lower logical efficiency) a programmable array for the realization of arbitrary switching functions. A second version of a sorting array, operating on a different sorting principle, is also described.

Index Terms—Cellular logic, large-scale integration, logic arrays logic in memory, push-down memory, sorting, switching functions.

Fig. 1. Cellular sorting array I.

$\hat{z} = M(x, \overline{y}, z) = x\overline{y} + z(x + \overline{y})$

## Processing in/near Memory: An Old Idea

Stone, "A Logic-in-Memory Computer," IEEE TC 1970.

#### A Logic-in-Memory Computer

HAROLD S. STONE

Abstract—If, as presently projected, the cost of microelectronic arrays in the future will tend to reflect the number of pins on the array rather than the number of gates, the logic-in-memory array is an extremely attractive computer component. Such an array is essentially a microelectronic memory with some combinational logic associated with each storage element.

## Why In-Memory Computation Today?

#### Huge problems with Memory Technology

- Memory technology scaling is not going well (e.g., RowHammer)

- Many scaling issues demand intelligence in memory

#### Huge demand from Applications & Systems

- Data access bottleneck

- Energy & power bottlenecks

- Data movement energy dominates computation energy

- Need all at the same time: performance, energy, sustainability

- We can improve all metrics by minimizing data movement

#### Designs are squeezed in the middle

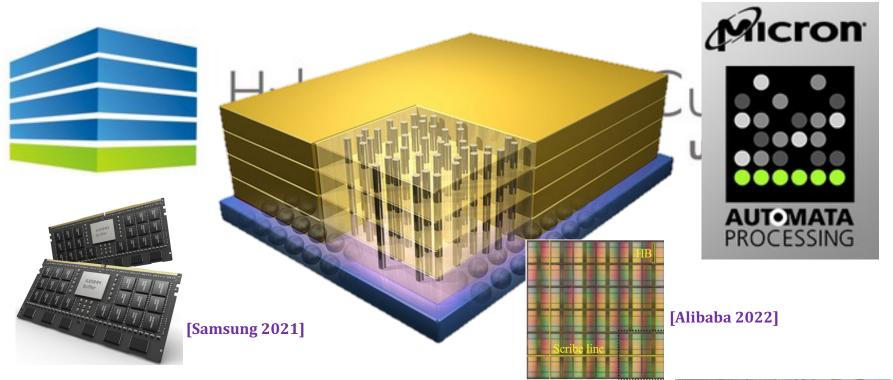

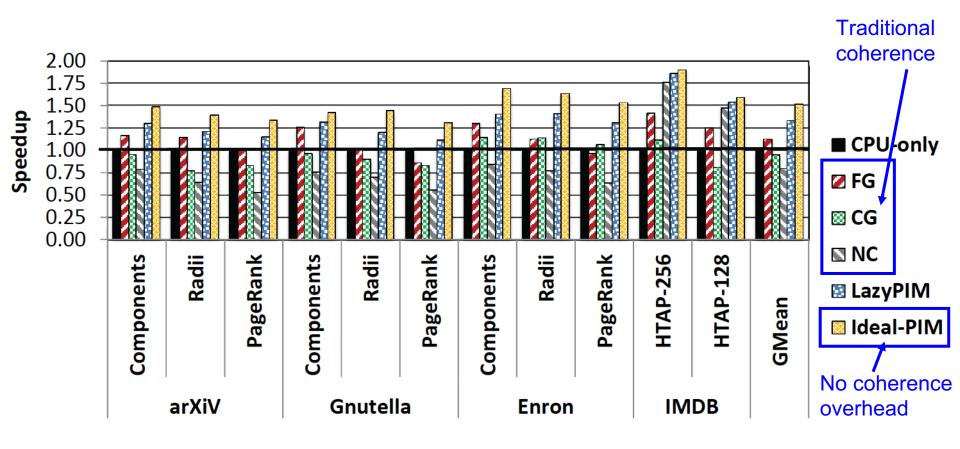

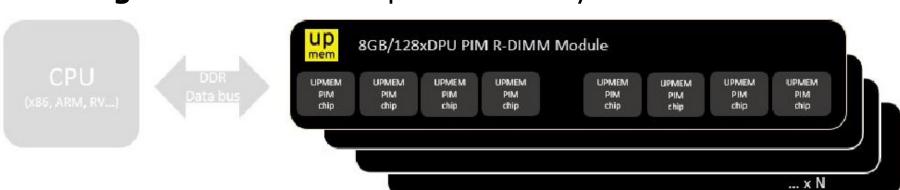

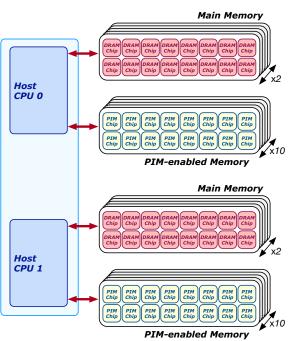

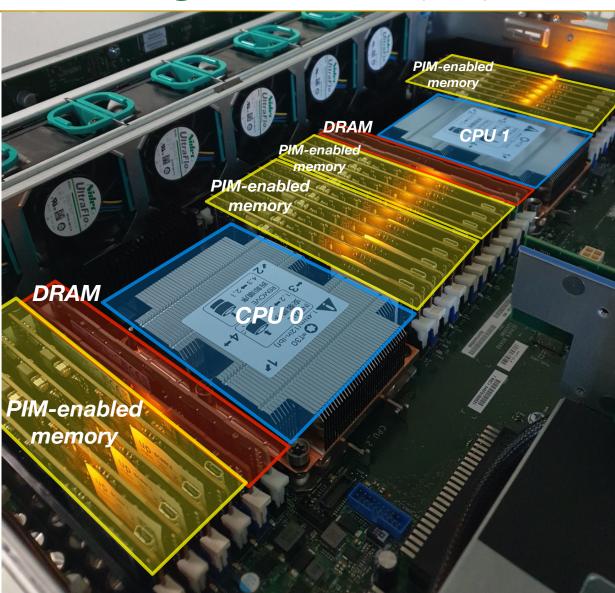

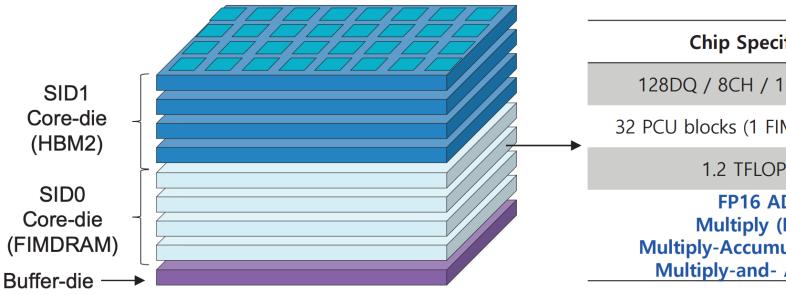

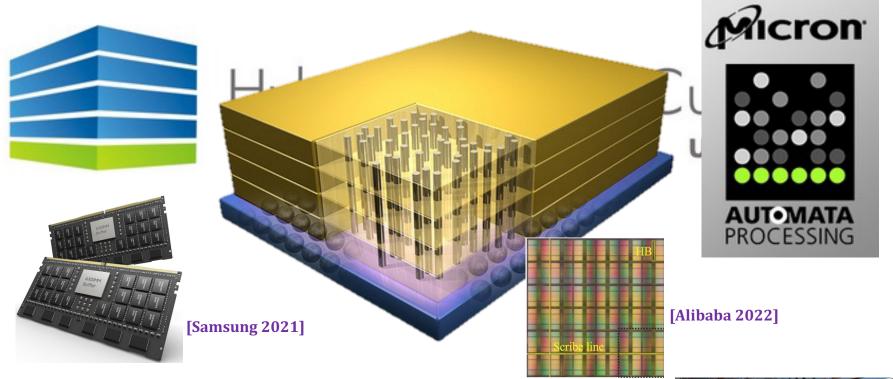

## Processing-in-Memory Landscape Today

**[Samsung 2021]**

[UPMEM 2019]

## Memory Scaling Issues Are Real

Onur Mutlu,

"Memory Scaling: A Systems Architecture Perspective"

Proceedings of the 5th International Memory

Workshop (IMW), Monterey, CA, May 2013. Slides

(pptx) (pdf)

EETimes Reprint

## Memory Scaling: A Systems Architecture Perspective

Onur Mutlu

Carnegie Mellon University

onur@cmu.edu

http://users.ece.cmu.edu/~omutlu/

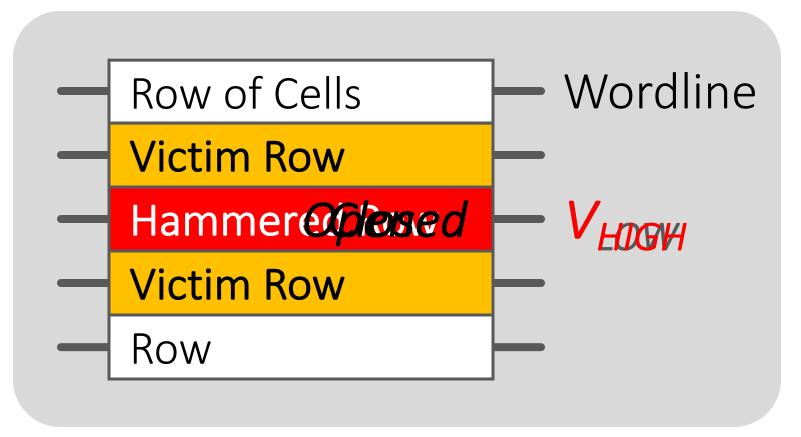

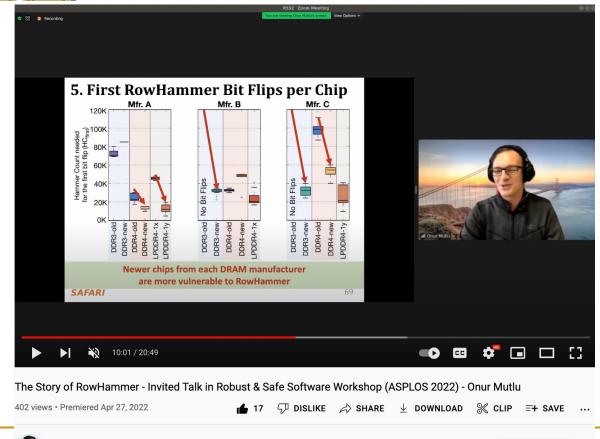

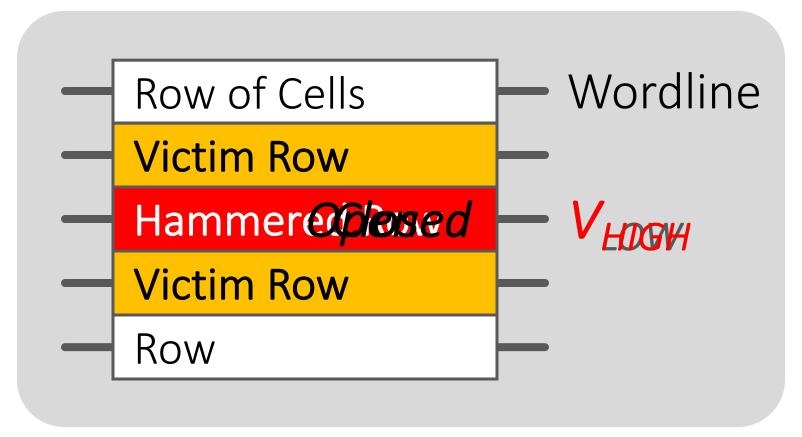

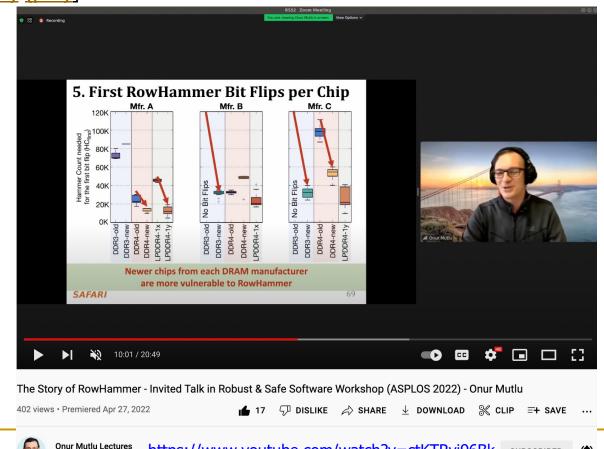

## A Curious Phenomenon [Kim et al., ISCA 2014]

# One can predictably induce errors in most DRAM memory chips

Kim+, "Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors," ISCA 2014.

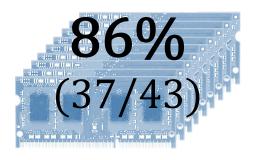

### Modern Memory is Prone to Disturbance Errors

Repeatedly reading a row enough times (before memory gets refreshed) induces disturbance errors in adjacent rows in most real DRAM chips you can buy today

### Most DRAM Modules Are Vulnerable

A company

**B** company

**C** company

Up to **1.0×10**<sup>7</sup>

errors

Up to **2.7×10**<sup>6</sup>

errors

Up to  $3.3 \times 10^5$  errors

## The RowHammer Vulnerability

## A simple hardware failure mechanism can create a widespread system security vulnerability

Forget Software—Now Hackers Are Exploiting Physics

BUSINESS CULTURE DESIGN GEAR SCIENCE

ANDY GREENBERG SECURITY 08.31.16 7:00 AM

# FORGET SOFTWARE—NOW HACKERS ARE EXPLOITING PHYSICS

### RowHammer [ISCA 2014]

Yoongu Kim, Ross Daly, Jeremie Kim, Chris Fallin, Ji Hye Lee, Donghyuk Lee, Chris Wilkerson, Konrad Lai, and Onur Mutlu,

<u>"Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors"</u>

Proceedings of the <u>41st International Symposium on Computer Architecture</u> (**ISCA**), Minneapolis, MN, June 2014.

[Slides (pptx) (pdf)] [Lightning Session Slides (pptx) (pdf)] [Source Code and Data] [Lecture Video (1 hr 49 mins), 25 September 2020]

One of the 7 papers of 2012-2017 selected as Top Picks in Hardware and Embedded Security for IEEE TCAD (<u>link</u>).

Selected to the ISCA-50 25-Year Retrospective Issue covering 1996-2020 in 2023 (Retrospective (pdf) Full Issue).

## Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors

Yoongu Kim<sup>1</sup> Ross Daly\* Jeremie Kim<sup>1</sup> Chris Fallin\* Ji Hye Lee<sup>1</sup> Donghyuk Lee<sup>1</sup> Chris Wilkerson<sup>2</sup> Konrad Lai Onur Mutlu<sup>1</sup>

<sup>1</sup>Carnegie Mellon University <sup>2</sup>Intel Labs

SAFARI

## Memory Scaling Issues Are Real

Onur Mutlu and Jeremie Kim,

"RowHammer: A Retrospective"

<u>IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems</u> (**TCAD**) Special Issue on Top Picks in Hardware and Embedded Security, 2019.

[Preliminary arXiv version]

[Slides from COSADE 2019 (pptx)]

[Slides from VLSI-SOC 2020 (pptx) (pdf)]

[Talk Video (1 hr 15 minutes, with Q&A)]

## RowHammer: A Retrospective

Onur Mutlu<sup>§‡</sup> Jeremie S. Kim<sup>‡§</sup> §ETH Zürich <sup>‡</sup>Carnegie Mellon University

SAFARI 64

## Memory Scaling Issues Are Real

Onur Mutlu, Ataberk Olgun, and A. Giray Yaglikci,

"Fundamentally Understanding and Solving RowHammer"

Invited Special Session Paper at the <u>28th Asia and South Pacific Design Automation Conference (ASP-DAC)</u>, Tokyo, Japan, January 2023.

[arXiv version]

[Slides (pptx) (pdf)]

[Talk Video (26 minutes)]

#### Fundamentally Understanding and Solving RowHammer

Onur Mutlu

onur.mutlu@safari.ethz.ch

ETH Zürich

Zürich, Switzerland

Ataberk Olgun ataberk.olgun@safari.ethz.ch ETH Zürich Zürich, Switzerland A. Giray Yağlıkcı giray.yaglikci@safari.ethz.ch ETH Zürich Zürich, Switzerland

#### Latest RowHammer Lecture

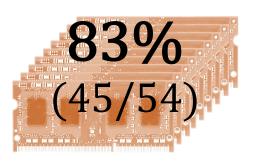

## The Story of RowHammer Tutorial ...

Onur Mutlu,

"Security Aspects of DRAM: The Story of RowHammer"

Invited Tutorial at 14th IEEE Electron Devices Society International Memory

Workshop (IMW), Dresden, Germany, May 2022.

[Slides (pptx)(pdf)]

[<u>Tutorial Video</u> (57 minutes)]

**EDIT VIDEO**

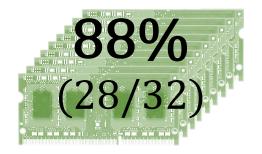

#### 10 Years of RowHammer in 20 Minutes

Onur Mutlu,

#### "The Story of RowHammer"

**Onur Mutlu Lectures**

24.5K subscribers

Invited Talk at the Workshop on Robust and Safe Software 2.0 (RSS2), held with the 27th International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS), Virtual, 28 February 2022.

[Slides (pptx) (pdf)]

# Main Memory Needs Intelligent Controllers

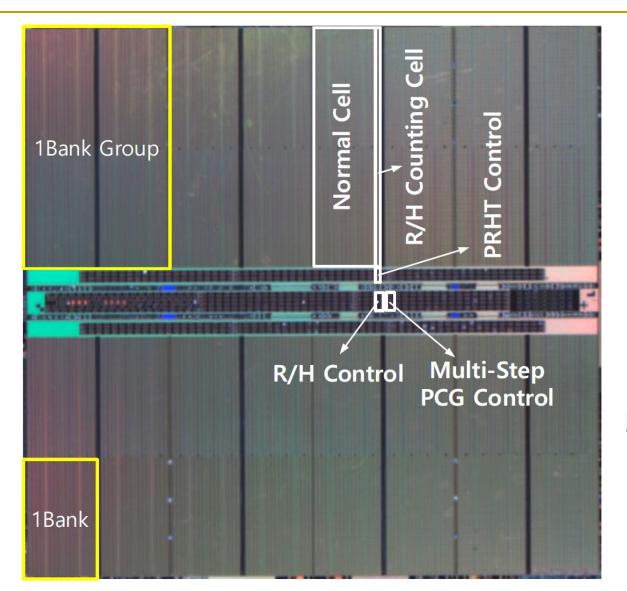

## Industry's Intelligent DRAM Controllers (I)

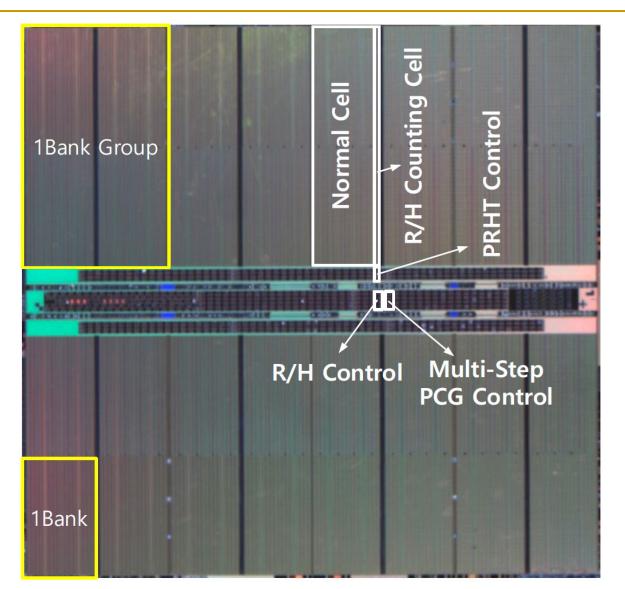

#### **ISSCC 2023 / SESSION 28 / HIGH-DENSITY MEMORIES /**

28.8 A 1.1V 16Gb DDR5 DRAM with Probabilistic-Aggressor Tracking, Refresh-Management Functionality, Per-Row Hammer Tracking, a Multi-Step Precharge, and Core-Bias Modulation for Security and Reliability Enhancement

Woongrae Kim, Chulmoon Jung, Seongnyuh Yoo, Duckhwa Hong, Jeongjin Hwang, Jungmin Yoon, Ohyong Jung, Joonwoo Choi, Sanga Hyun, Mankeun Kang, Sangho Lee, Dohong Kim, Sanghyun Ku, Donhyun Choi, Nogeun Joo, Sangwoo Yoon, Junseok Noh, Byeongyong Go, Cheolhoe Kim, Sunil Hwang, Mihyun Hwang, Seol-Min Yi, Hyungmin Kim, Sanghyuk Heo, Yeonsu Jang, Kyoungchul Jang, Shinho Chu, Yoonna Oh, Kwidong Kim, Junghyun Kim, Soohwan Kim, Jeongtae Hwang, Sangil Park, Junphyo Lee, Inchul Jeong, Joohwan Cho, Jonghwan Kim

SK hynix Semiconductor, Icheon, Korea

## Industry's Intelligent DRAM Controllers (II)

SK hynix Semiconductor, Icheon, Korea

DRAM products have been recently adopted in a wide range of high-performance computing applications: such as in cloud computing, in big data systems, and IoT devices. This demand creates larger memory capacity requirements, thereby requiring aggressive DRAM technology node scaling to reduce the cost per bit [1,2]. However, DRAM manufacturers are facing technology scaling challenges due to row hammer and refresh retention time beyond 1a-nm [2]. Row hammer is a failure mechanism, where repeatedly activating a DRAM row disturbs data in adjacent rows. Scaling down severely threatens reliability since a reduction of DRAM cell size leads to a reduction in the intrinsic row hammer tolerance [2,3]. To improve row hammer tolerance, there is a need to probabilistically activate adjacent rows with carefully sampled active addresses and to improve intrinsic row hammer tolerance [2]. In this paper, row-hammer-protection and refresh-management schemes are presented to guarantee DRAM security and reliability despite the aggressive scaling from 1a-nm to sub 10-nm nodes. The probabilisticaggressor-tracking scheme with a refresh-management function (RFM) and per-row hammer tracking (PRHT) improve DRAM resilience. A multi-step precharge reinforces intrinsic row-hammer tolerance and a core-bias modulation improves retention time: even in the face of cell-transistor degradation due to technology scaling. This comprehensive scheme leads to a reduced probability of failure, due to row hammer attacks, by 93.1% and an improvement in retention time by 17%.

## Industry's Intelligent DRAM Controllers (III)

#### ISSCC 2023 / SESSION 28 / HIGH-DENSITY MEMORIES

28.8 A 1.1V 16Gb DDR5 DRAM with Probabilistic-Aggressor Tracking, Refresh-Management Functionality, Per-Row Hammer Tracking, a Multi-Step Precharge, and Core-Bias Modulation for Security and Reliability Enhancement

Woongrae Kim, Chulmoon Jung, Seongnyuh Yoo, Duckhwa Hong, Jeongjin Hwang, Jungmin Yoon, Ohyong Jung, Joonwoo Choi, Sanga Hyun, Mankeun Kang, Sangho Lee, Dohong Kim, Sanghyun Ku, Donhyun Choi, Nogeun Joo, Sangwoo Yoon, Junseok Noh, Byeongyong Go, Cheolhoe Kim, Sunil Hwang, Mihyun Hwang, Seol-Min Yi, Hyungmin Kim, Sanghyuk Heo, Yeonsu Jang, Kyoungchul Jang, Shinho Chu, Yoonna Oh, Kwidong Kim, Junghyun Kim, Soohwan Kim, Jeongtae Hwang, Sangil Park, Junphyo Lee, Inchul Jeong, Joohwan Cho, Jonghwan Kim

SK hynix Semiconductor, Icheon, Korea

## Industry's Intelligent DRAM Controllers (IV)

## DSAC: Low-Cost Rowhammer Mitigation Using In-DRAM Stochastic and Approximate Counting Algorithm

Seungki Hong Dongha Kim Jaehyung Lee Reum Oh Changsik Yoo Sangjoon Hwang Jooyoung Lee

DRAM Design Team, Memory Division, Samsung Electronics

https://arxiv.org/pdf/2302.03591v1.pdf

## Are We Now BitFlip Free?

Appears at ISCA 2023

## RowPress: Amplifying Read-Disturbance in Modern DRAM Chips

Haocong Luo Ataberk Olgun A. Giray Yağlıkçı Yahya Can Tuğrul Steve Rhyner Meryem Banu Cavlak Joël Lindegger Mohammad Sadrosadati Onur Mutlu ETH Zürich

74

## RowPress [ISCA 2023]

Haocong Luo, Ataberk Olgun, Giray Yaglikci, Yahya Can Tugrul, Steve Rhyner,

M. Banu Cavlak, Joel Lindegger, Mohammad Sadrosadati, and Onur Mutlu,

"RowPress: Amplifying Read Disturbance in Modern DRAM Chips"

Proceedings of the <u>50th International Symposium on Computer</u> <u>Architecture</u> (**ISCA**), Orlando, FL, USA, June 2023.

[Slides (pptx) (pdf)]

[Lightning Talk Slides (pptx) (pdf)]

[<u>Lightning Talk Video</u> (3 minutes)]

[RowPress Source Code and Datasets (Officially Artifact Evaluated with All Badges)]

Officially artifact evaluated as available, reusable and reproducible. Best artifact award at ISCA 2023.

## RowPress: Amplifying Read-Disturbance in Modern DRAM Chips

Haocong Luo Ataberk Olgun A. Giray Yağlıkçı Yahya Can Tuğrul Steve Rhyner Meryem Banu Cavlak Joël Lindegger Mohammad Sadrosadati Onur Mutlu

ETH Zürich

#### Emerging Memories Also Need Intelligent Controllers

Benjamin C. Lee, Engin Ipek, Onur Mutlu, and Doug Burger,

"Architecting Phase Change Memory as a Scalable DRAM Alternative"

Proceedings of the 36th International Symposium on Computer

Architecture (ISCA), pages 2-13, Austin, TX, June 2009. Slides (pdf)

One of the 13 computer architecture papers of 2009 selected as Top

Picks by IEEE Micro. Selected as a CACM Research Highlight.

2022 Persistent Impact Prize.

#### Architecting Phase Change Memory as a Scalable DRAM Alternative

Benjamin C. Lee† Engin Ipek† Onur Mutlu‡ Doug Burger†

†Computer Architecture Group Microsoft Research Redmond, WA {blee, ipek, dburger}@microsoft.com ‡Computer Architecture Laboratory Carnegie Mellon University Pittsburgh, PA onur@cmu.edu

## Intelligent Memory Controllers Can Avoid Many Failures & Enable Better Scaling

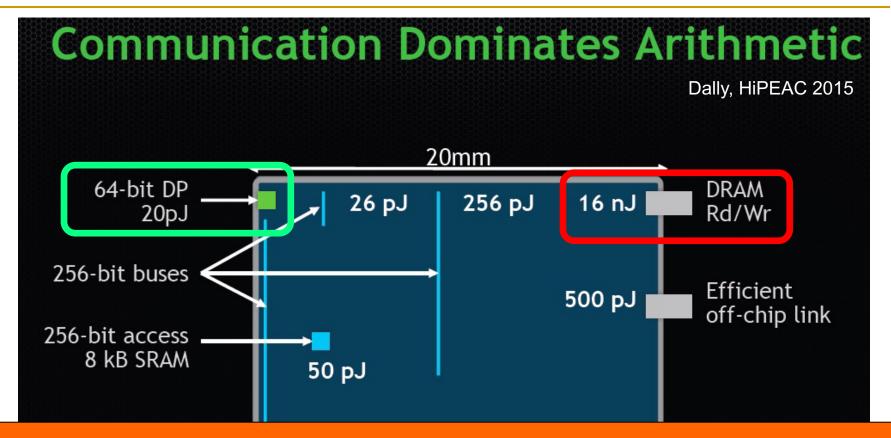

## Three Key Systems & Application Trends

### 1. **Data access** is the major bottleneck

Applications are increasingly data hungry

#### 2. **Energy** consumption is a key limiter

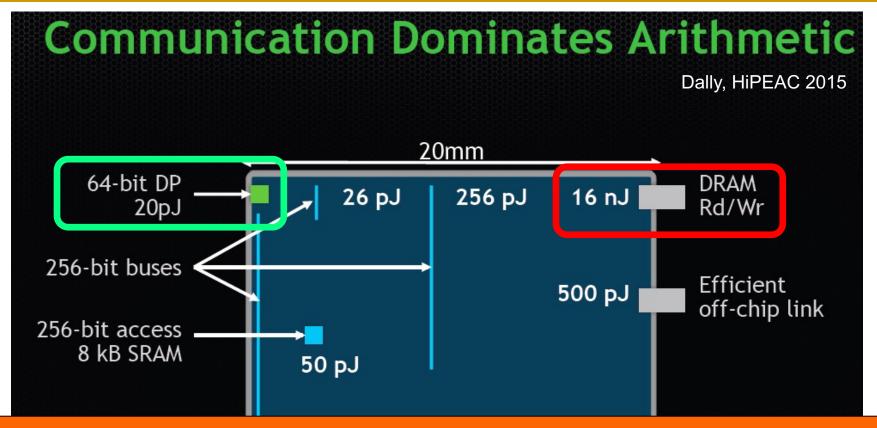

## 3. Data movement energy dominates compute

Especially true for off-chip to on-chip movement

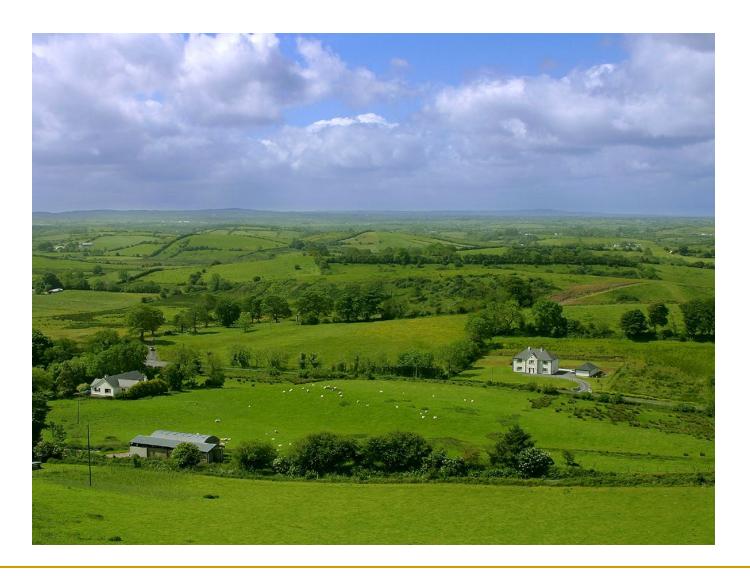

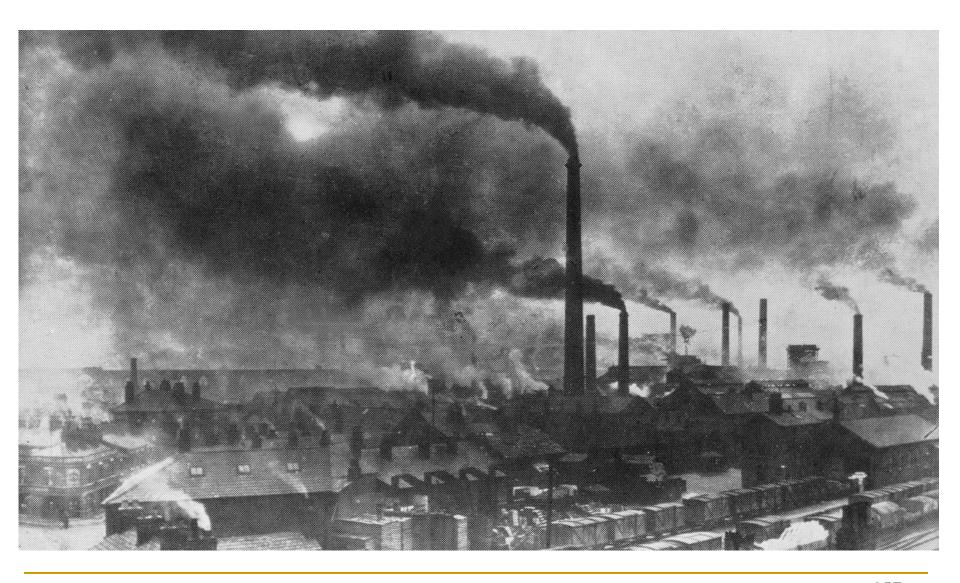

## Do We Want This?

79

## Or This?

**SAFARI**

80

High Performance, Energy Efficient, Sustainable (All at the Same Time)

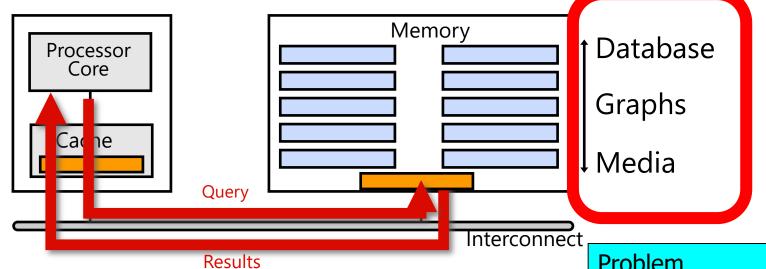

#### The Problem

Data access is the major performance and energy bottleneck

# Our current design principles cause great energy waste

(and great performance loss)

# Processing of data is performed far away from the data

## Today's Computing Systems

- Processor centric

- All data processed in the processor → at great system cost

## It's the Memory, Stupid!

"It's the Memory, Stupid!" (Richard Sites, MPR, 1996)

#### RICHARD SITES

#### It's the Memory, Stupid!

When we started the Alpha architecture design in 1988, we estimated a 25-year lifetime and a relatively modest 32% per year compounded performance improvement of implementations over that lifetime (1,000× total). We guestimated about 10× would come from CPU clock improvement, 10× from multiple instruction issue, and 10× from multiple processors.

I expect that over the coming decade memory subsystem design will be the *only* important design issue for microprocessors.

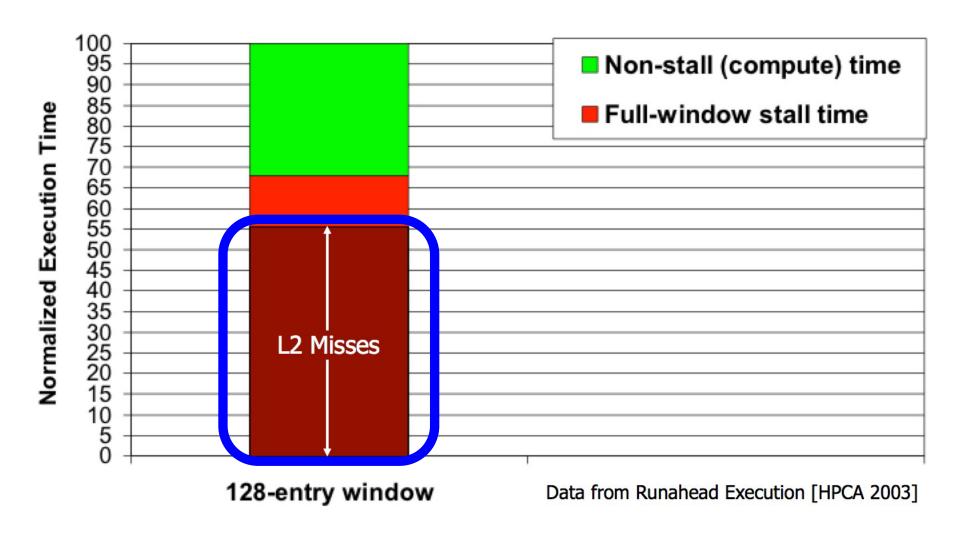

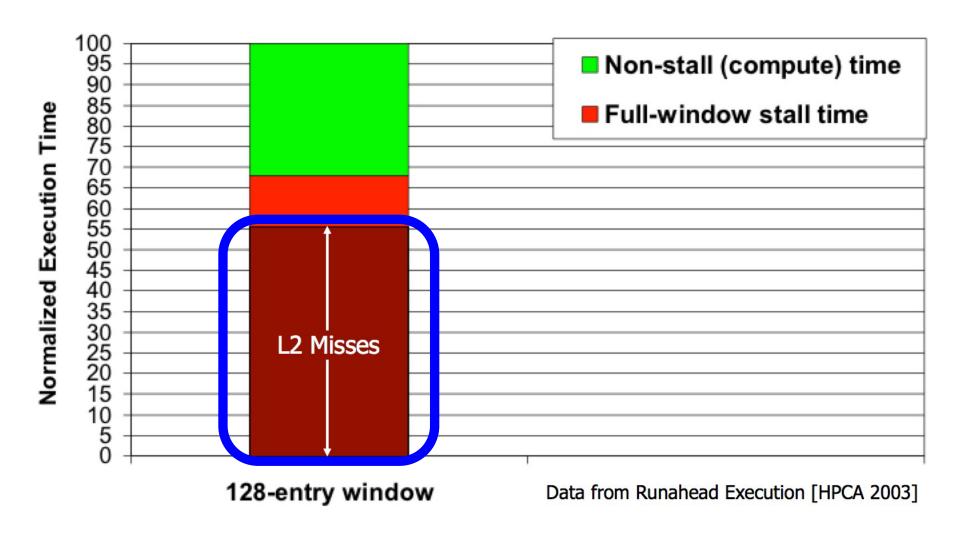

## The Performance Perspective

## The Performance Perspective

Onur Mutlu, Jared Stark, Chris Wilkerson, and Yale N. Patt,

"Runahead Execution: An Alternative to Very Large Instruction Windows for Out-of-order Processors"

Proceedings of the <u>9th International Symposium on High-Performance Computer</u>

<u>Architecture</u> (**HPCA**), pages 129-140, Anaheim, CA, February 2003. <u>Slides (pdf)</u>

<u>One of the 15 computer arch. papers of 2003 selected as Top Picks by IEEE Micro.</u>

<u>HPCA Test of Time Award (awarded in 2021).</u>

#### Runahead Execution: An Alternative to Very Large Instruction Windows for Out-of-order Processors

Onur Mutlu § Jared Stark † Chris Wilkerson ‡ Yale N. Patt §

§ECE Department

The University of Texas at Austin

{onur,patt}@ece.utexas.edu

†Microprocessor Research Intel Labs jared.w.stark@intel.com

‡Desktop Platforms Group Intel Corporation chris.wilkerson@intel.com

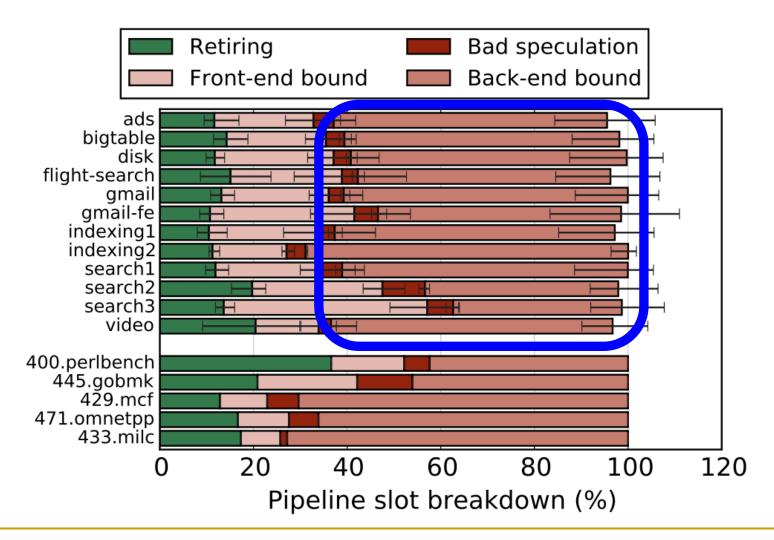

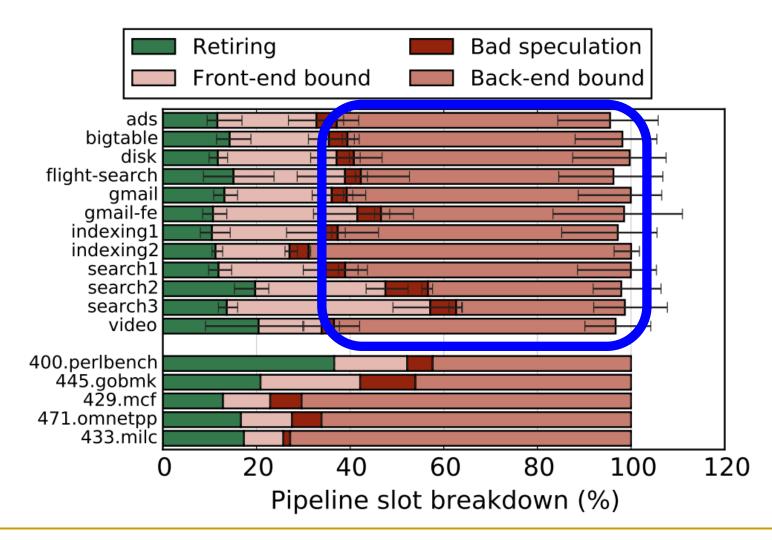

## The Performance Perspective (Today)

All of Google's Data Center Workloads (2015):

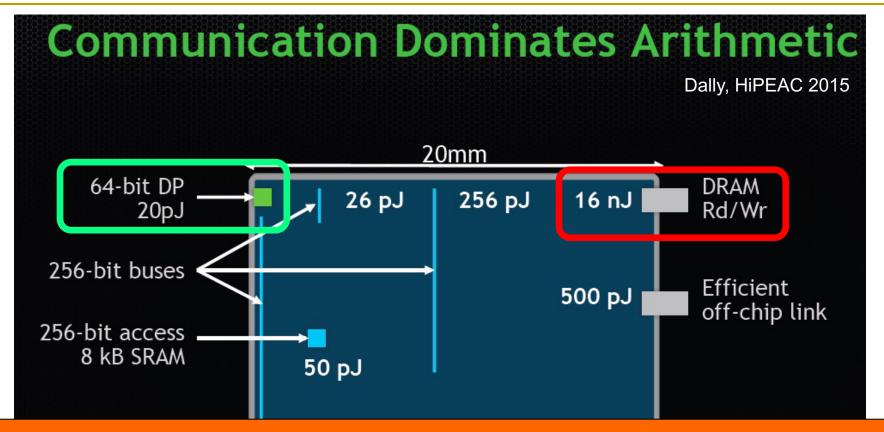

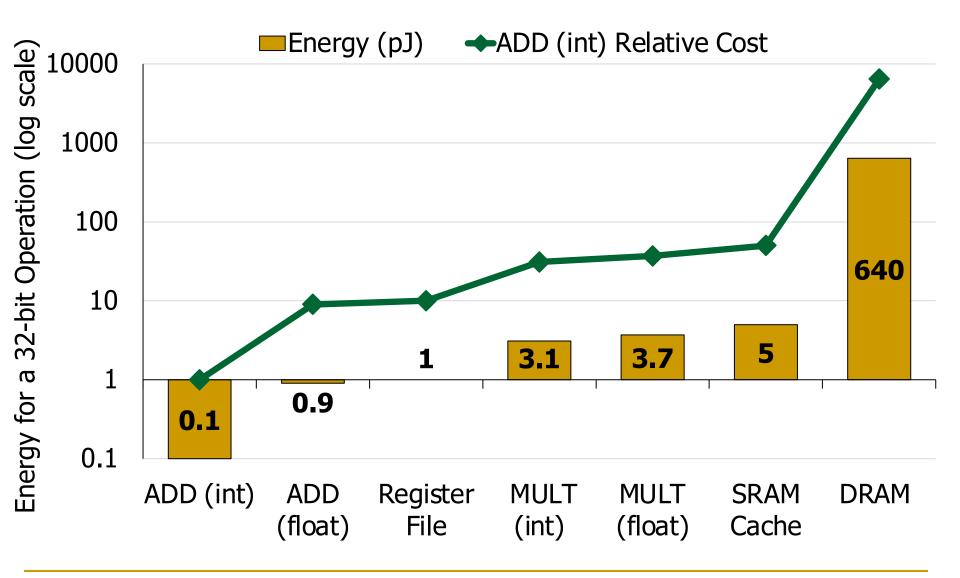

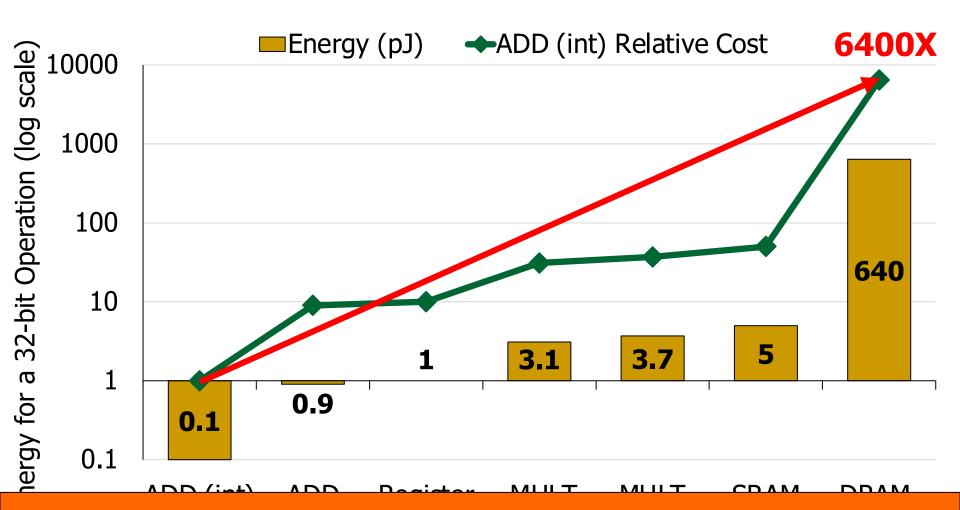

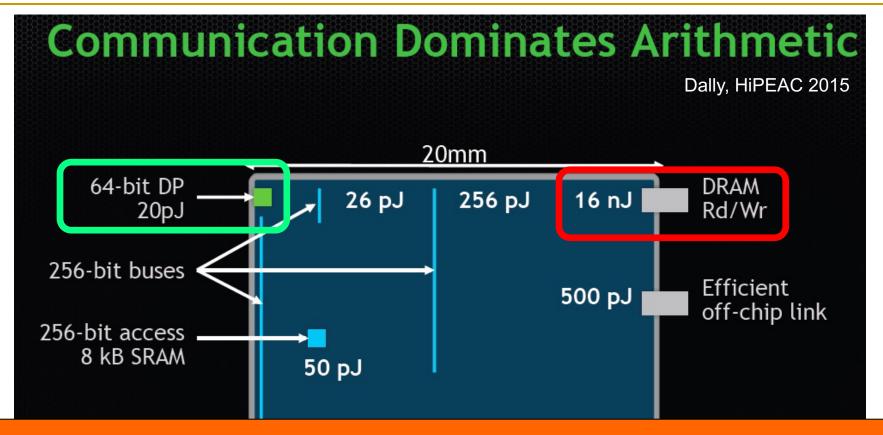

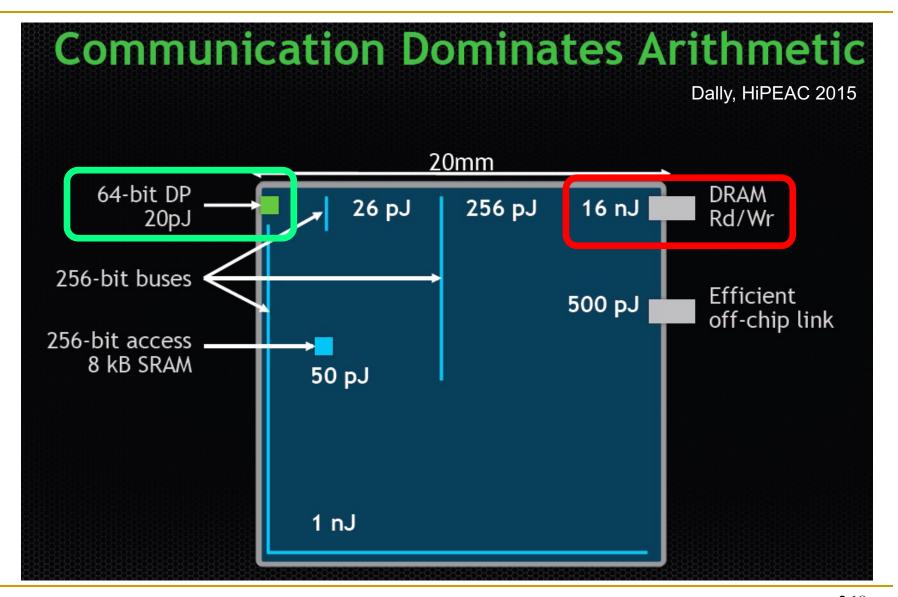

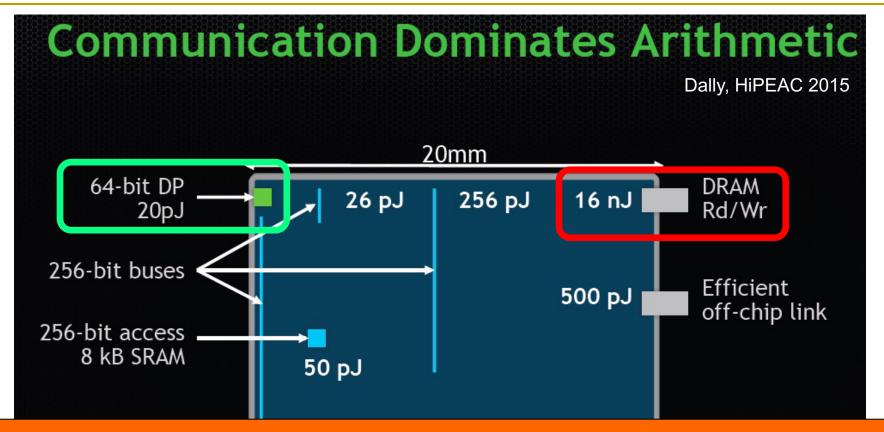

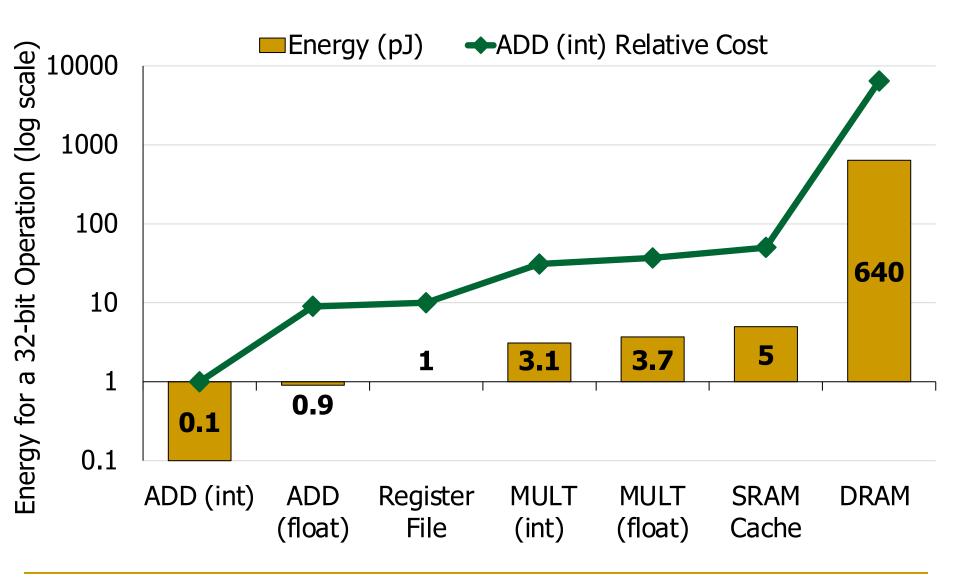

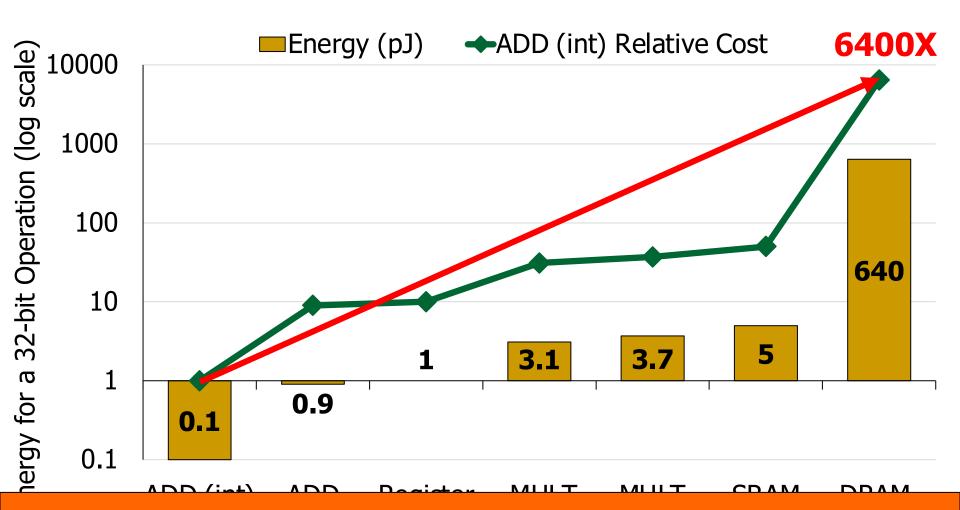

## Data Movement vs. Computation Energy

A memory access consumes ~100-1000X the energy of a complex addition

## Data Movement vs. Computation Energy

## Data Movement vs. Computation Energy

A memory access consumes 6400X the energy of a simple integer addition

### Energy Waste in Mobile Devices

Amirali Boroumand, Saugata Ghose, Youngsok Kim, Rachata Ausavarungnirun, Eric Shiu, Rahul Thakur, Daehyun Kim, Aki Kuusela, Allan Knies, Parthasarathy Ranganathan, and Onur Mutlu, "Google Workloads for Consumer Devices: Mitigating Data Movement Bottlenecks" Proceedings of the 23rd International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS), Williamsburg, VA, USA, March 2018.

## 62.7% of the total system energy is spent on data movement

## Google Workloads for Consumer Devices: Mitigating Data Movement Bottlenecks

Amirali Boroumand<sup>1</sup> Saugata Ghose<sup>1</sup> Youngsok Kim<sup>2</sup> Rachata Ausavarungnirun<sup>1</sup> Eric Shiu<sup>3</sup> Rahul Thakur<sup>3</sup> Daehyun Kim<sup>4,3</sup> Aki Kuusela<sup>3</sup> Allan Knies<sup>3</sup> Parthasarathy Ranganathan<sup>3</sup> Onur Mutlu<sup>5,1</sup>

SAFARI

## Energy Waste in Accelerators

Amirali Boroumand, Saugata Ghose, Berkin Akin, Ravi Narayanaswami, Geraldo F. Oliveira,

Xiaoyu Ma, Eric Shiu, and Onur Mutlu,

"Google Neural Network Models for Edge Devices: Analyzing and Mitigating Machine Learning Inference Bottlenecks"

Proceedings of the <u>30th International Conference on Parallel Architectures and Compilation</u> <u>Techniques</u> (**PACT**), Virtual, September 2021.

[Slides (pptx) (pdf)]

[Talk Video (14 minutes)]

## > 90% of the total system energy is spent on memory in large ML models

#### Google Neural Network Models for Edge Devices: Analyzing and Mitigating Machine Learning Inference Bottlenecks

Amirali Boroumand<sup>†</sup>

Saugata Ghose<sup>‡</sup>

Berkin Akin<sup>§</sup>

Ravi Narayanaswami<sup>§</sup>

Geraldo F. Oliveira<sup>⋆</sup>

Xiaoyu Ma<sup>§</sup>

Eric Shiu<sup>§</sup>

Onur Mutlu<sup>⋆†</sup>

†Carnegie Mellon Univ.

Stanford Univ.

Univ. of Illinois Urbana-Champaign

Google \*ETH Zürich\*

SAFARI

#### We Do Not Want to Move Data!

A memory access consumes ~100-1000X the energy of a complex addition

#### We Do Not Want to Move Data!

A memory access consumes ~100-1000X the energy of a complex addition

## We Need A Paradigm Shift To ...

Enable computation with minimal data movement

Compute where it makes sense (where data resides)

Make computing architectures more data-centric

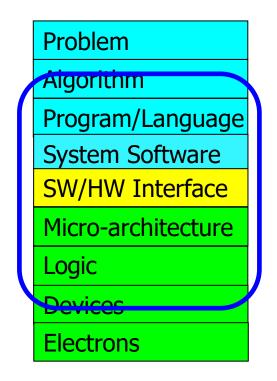

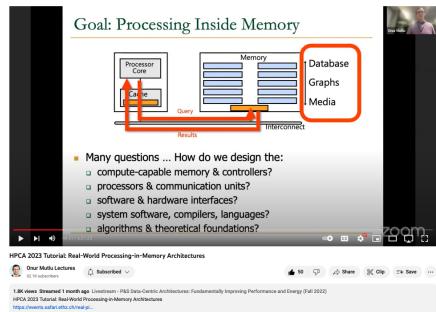

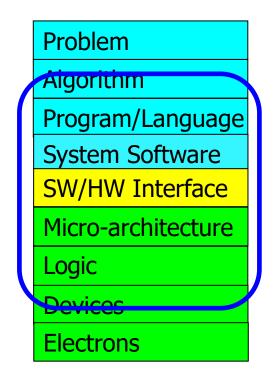

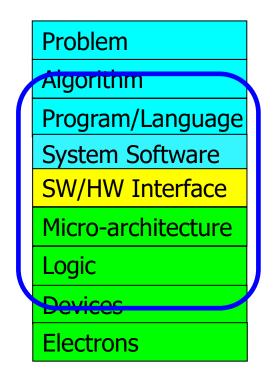

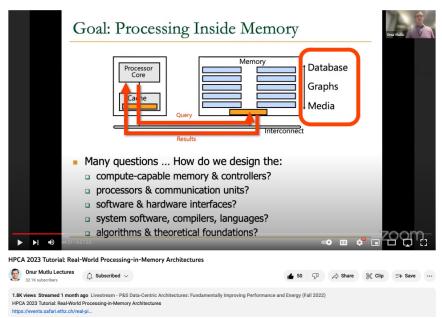

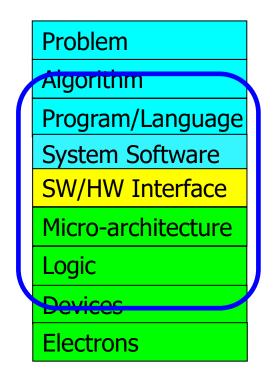

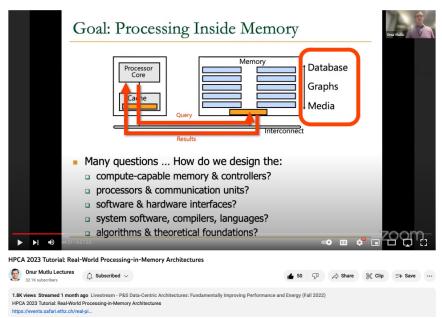

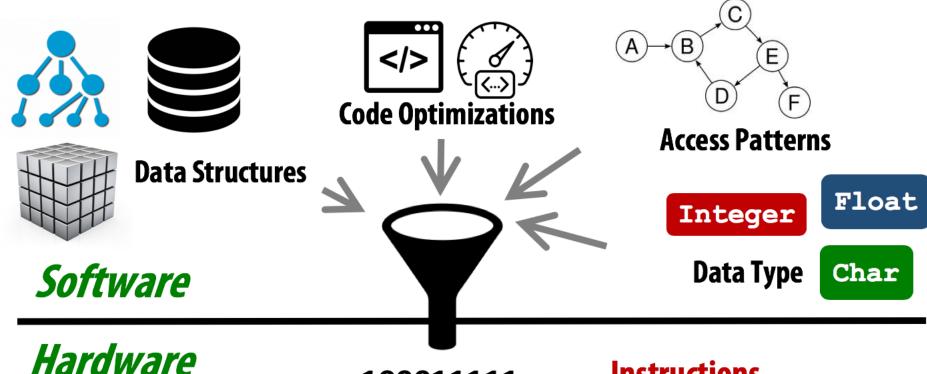

## Goal: Processing Inside Memory/Storage

- Many questions ... How do we design the:

- compute-capable memory & controllers?

- processors & communication units?

- software & hardware interfaces?

- system software, compilers, languages?

- algorithms & theoretical foundations?

**Problem**

Algorithm

Program/Language

System Software

SW/HW Interface

Micro-architecture

Logic

Electrons

## PIM Review and Open Problems

## A Modern Primer on Processing in Memory

Onur Mutlu<sup>a,b</sup>, Saugata Ghose<sup>b,c</sup>, Juan Gómez-Luna<sup>a</sup>, Rachata Ausavarungnirun<sup>d</sup>

SAFARI Research Group

<sup>a</sup>ETH Zürich

<sup>b</sup>Carnegie Mellon University

<sup>c</sup>University of Illinois at Urbana-Champaign

<sup>d</sup>King Mongkut's University of Technology North Bangkok

Onur Mutlu, Saugata Ghose, Juan Gomez-Luna, and Rachata Ausavarungnirun,

"A Modern Primer on Processing in Memory"

Invited Book Chapter in Emerging Computing: From Devices to Systems

Looking Beyond Moore and Von Neumann, Springer, to be published in 2021.

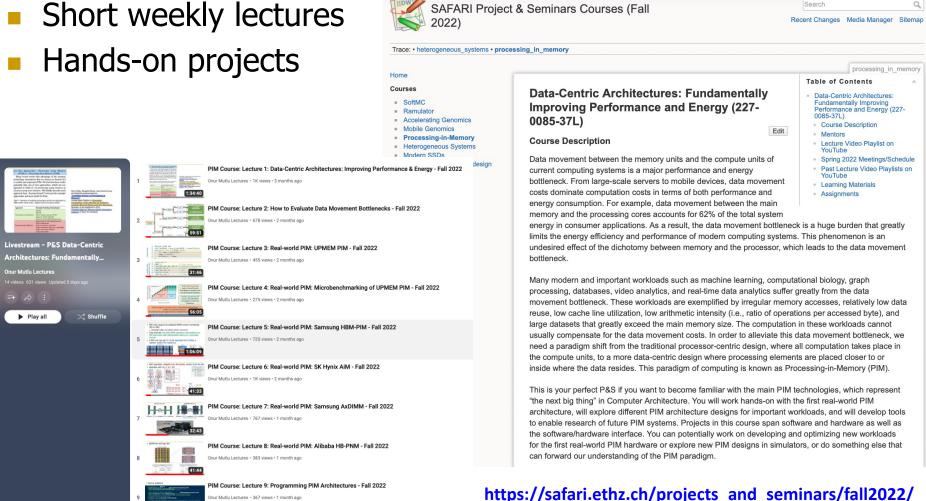

### PIM Course (Fall 2022)

#### Fall 2022 Edition:

https://safari.ethz.ch/projects and seminars/fall2022 /doku.php?id=processing in memory

#### Spring 2022 Edition:

https://safari.ethz.ch/projects and seminars/spring2 022/doku.php?id=processing in memory

#### Youtube Livestream (Fall 2022):

https://www.youtube.com/watch?v=QLL0wQ9I4Dw& list=PL5Q2soXY2Zi8KzG2CQYRNQOVD0GOBrnKy

#### Youtube Livestream (Spring 2022):

https://www.youtube.com/watch?v=9e4Chnwdovo&li st=PL5Q2soXY2Zi-841fUYYUK9EsXKhQKRPyX

#### Project course

- Taken by Bachelor's/Master's students

- Processing-in-Memory lectures

- Hands-on research exploration

- Many research readings

https://www.youtube.com/onurmutlulectures

#### Spring 2022 Meetings/Schedule

| Week | Date          | Livestream       | Meeting                                                                        | Learning<br>Materials                          | Assignments |

|------|---------------|------------------|--------------------------------------------------------------------------------|------------------------------------------------|-------------|

| W1   | 10.03<br>Thu. | You Live         | M1: P&S PIM Course Presentation (PDF) (PPT)                                    | Required Materials<br>Recommended<br>Materials | HW 0 Out    |

| W2   | 15.03<br>Tue. |                  | Hands-on Project Proposals                                                     |                                                |             |

|      | 17.03<br>Thu. | You Premiere     | M2: Real-world PIM: UPMEM PIM                                                  |                                                |             |

| W3   | 24.03<br>Thu. | You Live         | M3: Real-world PIM:<br>Microbenchmarking of UPMEM<br>PIM<br>cm (PDF) am (PPT)  |                                                |             |

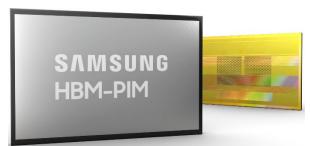

| W4   | 31.03<br>Thu. | You the Live     | M4: Real-world PIM: Samsung<br>HBM-PIM<br>(PDF) (PPT)                          |                                                |             |

| W5   | 07.04<br>Thu. | You the Live     | M5: How to Evaluate Data<br>Movement Bottlenecks<br>(CDF) an (PPT)             |                                                |             |

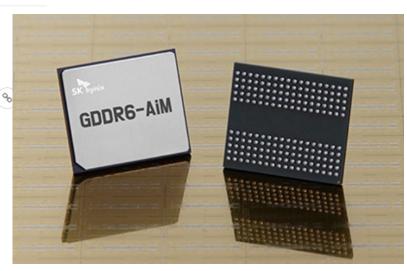

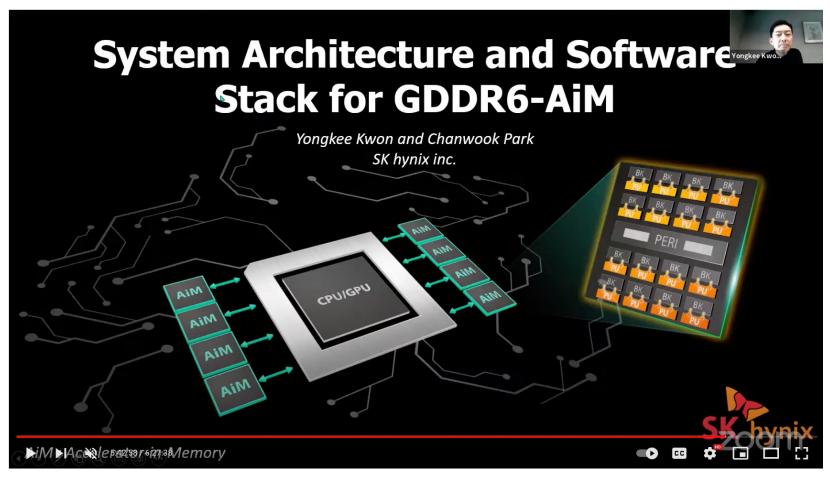

| W6   | 14.04<br>Thu. | You Live         | M6: Real-world PIM: SK Hynix AiM                                               |                                                |             |

| W7   | 21.04<br>Thu. | You the Premiere | M7: Programming PIM<br>Architectures<br>(m) (PDF) (m) (PPT)                    |                                                |             |

| W8   | 28.04<br>Thu. | You Premiere     | M8: Benchmarking and Workload<br>Suitability on PIM<br>(CDF) and (PDF)         |                                                |             |

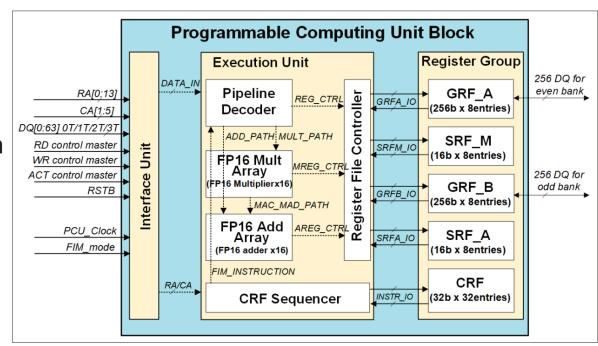

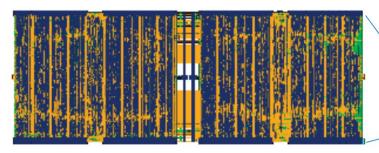

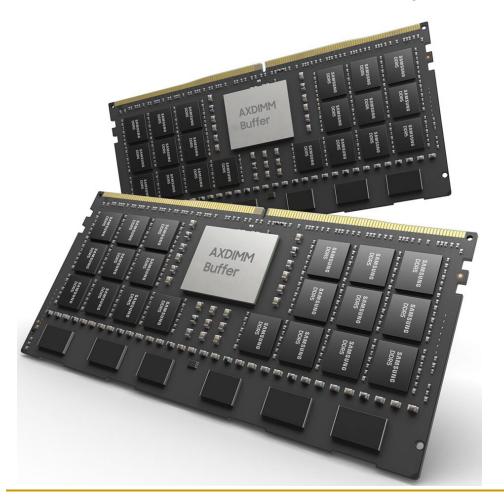

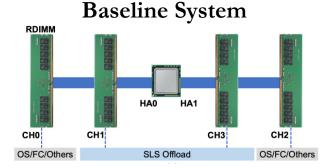

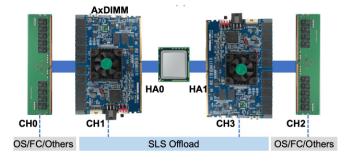

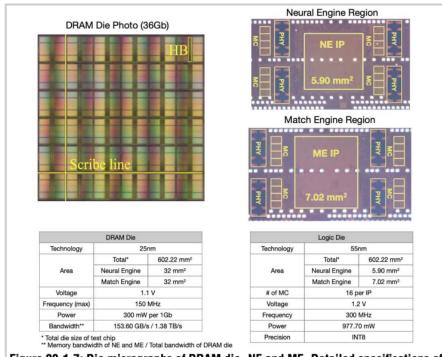

| W9   | 05.05<br>Thu. | You Premiere     | M9: Real-world PIM: Samsung<br>AxDIMM<br>(ERI (PDF) (ERI (PPT)                 |                                                |             |

| W10  | 12.05<br>Thu. | You Premiere     | M10: Real-world PIM: Alibaba HB-<br>PNM<br>(EDF) aan (PPT)                     |                                                |             |

| W11  | 19.05<br>Thu. | You Live         | M11: SpMV on a Real PIM<br>Architecture                                        |                                                |             |

| W12  | 26.05<br>Thu. | You the Live     | M12: End-to-End Framework for<br>Processing-using-Memory<br>(R) (PDF) am (PPT) |                                                |             |

| W13  | 02.06<br>Thu. | You Live         | M13: Bit-Serial SIMD Processing using DRAM (PDF) (PPT)                         |                                                |             |

| W14  | 09.06<br>Thu. | You the Live     | M14: Analyzing and Mitigating ML<br>Inference Bottlenecks<br>(CDF) am (PPT)    |                                                |             |

| W15  | 15.06<br>Thu. | You the Live     | M15: In-Memory HTAP Databases<br>with HW/SW Co-design<br>(CDF) (PDF) (PPT)     |                                                |             |

| W16  | 23.06<br>Thu. | You tobe Live    | M16: In-Storage Processing for<br>Genome Analysis<br>(PDF) arr (PPT)           |                                                |             |

| W17  | 18.07<br>Mon. | You the Premiere | M17: How to Enable the Adoption of PIM2                                        |                                                |             |

| W18  | 09.08<br>Tue. | You the Premiere | SS1: ISVLSI 2022 Special Session on PIM (PDF & PPT)                            |                                                |             |

## SSD Course (Spring 2023)

#### Spring 2023 Edition:

https://safari.ethz.ch/projects and seminars/spring2023/ doku.php?id=modern\_ssds

#### Fall 2022 Edition:

https://safari.ethz.ch/projects and seminars/fall2022/do ku.php?id=modern ssds

#### Youtube Livestream (Spring 2023):

https://www.youtube.com/watch?v=4VTwOMmsnJY&list =PL5Q2soXY2Zi 8qOM5Icpp8hB2SHtm4z57&pp=iAQB

#### Youtube Livestream (Fall 2022):

https://www.youtube.com/watch?v=hqLrd-Uj0aU&list=PL5Q2soXY2Zi9BJhenUq4JI5bwhAMpAp13&p p=iAOB

#### Project course

- Taken by Bachelor's/Master's students

- SSD Basics and Advanced Topics

- Hands-on research exploration

- Many research readings

#### Fall 2022 Meetings/Schedule

| Week | Date       | Livestream         | Meeting                                                                                                                                                  | Learning<br>Materials   | Assignments |

|------|------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------|

| W1   | 06.10      |                    | M1: P&S Course Presentation                                                                                                                              | Required<br>Recommended |             |

| W2   | 12.10      | You Time Live      | M2: Basics of NAND Flash-<br>Based SSDs                                                                                                                  | Required<br>Recommended |             |

| W3   | 19.10      | YouTube Live       | M3: NAND Flash Read/Write<br>Operations<br>ma PDF ma PPT                                                                                                 | Required<br>Recommended |             |

| W4   | 26.10      | You Ture Live      | M4: Processing inside NAND<br>Flash<br>ma PDF ma PPT                                                                                                     | Required<br>Recommended |             |

| W5   | 02.11      | You Time Live      | M5: Advanced NAND Flash<br>Commands & Mapping                                                                                                            | Required<br>Recommended |             |

| W6   | 09.11      | You Tute Live      | M6: Processing inside Storage                                                                                                                            | Required<br>Recommended |             |

| W7   | 23.11      | You Tibe Live      | M7: Address Mapping &<br>Garbage Collection                                                                                                              | Required<br>Recommended |             |

| W8   | 30.11      | You Tute Live      | M8: Introduction to MQSim                                                                                                                                | Required<br>Recommended |             |

| W9   | 14.12      | You Tipe Live      | M9: Fine-Grained Mapping and<br>Multi-Plane Operation-Aware<br>Block Management                                                                          | Required<br>Recommended |             |

| W10  | 04.01.2023 | You Time Premiere  | M10a: NAND Flash Basics                                                                                                                                  | Required<br>Recommended |             |

|      |            |                    | M10b: Reducing Solid-State Drive Read Latency by Optimizing Read-Retry DPF im PPT imPaper                                                                | Required<br>Recommended |             |

|      |            |                    | M10c: Evanesco: Architectural<br>Support for Efficient Data<br>Sanitization in Modern Flash-<br>Based Storage Systems<br>MPDF mPPT mPaper                | Required<br>Recommended |             |

|      |            |                    | M10d; DeepSketch: A New<br>Machine Learning-Based<br>Reference Search Technique<br>for Post-Deduplication Delta<br>Compression<br>ma PDF ma PPT ma Paper | Required<br>Recommended |             |

| W11  | 11.01      | You Tive           | M11: FLIN: Enabling Fairness<br>and Enhancing Performance in<br>Modern NVMe Solid State<br>Drives<br>mPDF mPPT                                           | Required                |             |

| W12  | 25.01      | You Title Premiere | M12: Flash Memory and Solid-<br>State Drives                                                                                                             | Recommended             |             |

#### https://www.youtube.com/onurmutlulectures

## Genomics Course (Fall 2022)

#### Fall 2022 Edition:

https://safari.ethz.ch/projects and seminars/fall2022/do ku.php?id=bioinformatics

#### Spring 2022 Edition:

https://safari.ethz.ch/projects and seminars/spring2022/doku.php?id=bioinformatics

#### Youtube Livestream (Fall 2022):

https://www.youtube.com/watch?v=nA41964-9r8&list=PL5Q2soXY2Zi8tFlQvdxOdizD\_EhVAMVQV

#### Youtube Livestream (Spring 2022):

https://www.youtube.com/watch?v=DEL\_5A\_Y3TI&list= PL5Q2soXY2Zi8NrPDqOR1yRU\_Cxxjw-u18

#### Project course

- Taken by Bachelor's/Master's students

- Genomics lectures

- Hands-on research exploration

- Many research readings

https://www.youtube.com/onurmutlulectures

#### Spring 2022 Meetings/Schedule

| Week | Date          | Livestream        | Meeting                                                                           | Learning<br>Materials                             |

|------|---------------|-------------------|-----------------------------------------------------------------------------------|---------------------------------------------------|

| W1   | 11.3<br>Fri.  | You Tube Live     | M1: P&S Accelerating Genomics Course Introduction & Project Proposals (PDF) (PPT) | Required<br>Materials<br>Recommended<br>Materials |

| W2   | 18.3<br>Fri.  | You Tube Live     | M2: Introduction to Sequencing (PDF) (PPT)                                        |                                                   |

| W3   | 25.3<br>Fri.  | You Tube Premiere | M3: Read Mapping  (PDF) (PPT)                                                     |                                                   |

| W4   | 01.04<br>Fri. | You Tube Premiere | M4: GateKeeper  (PDF) (PPT)                                                       |                                                   |

| W5   | 08.04<br>Fri. | You Tube Premiere | M5: MAGNET & Shouji (PDF) (PPT)                                                   |                                                   |

| W6   | 15.4<br>Fri.  | You Tube Premiere | M6: SneakySnake  (PDF) (PPT)                                                      |                                                   |

| W7   | 29.4<br>Fri.  | You Tube Premiere | M7: GenStore (PDF) (PPT)                                                          |                                                   |

| W8   | 06.05<br>Fri. | You Tube Premiere | M8: GRIM-Filter  (PDF) (PPT)                                                      |                                                   |

| W9   | 13.05<br>Fri. | You Tube Premiere | M9: Genome Assembly  (PDF) (PPT)                                                  |                                                   |

| W10  | 20.05<br>Fri. | You Tube Live     | M10: Genomic Data Sharing Under Differential Privacy (PDF) (PPT)                  |                                                   |

| W11  | 10.06<br>Fri. | You Tube Premiere | M11: Accelerating Genome<br>Sequence Analysis<br>(PDF) (PPT)                      |                                                   |

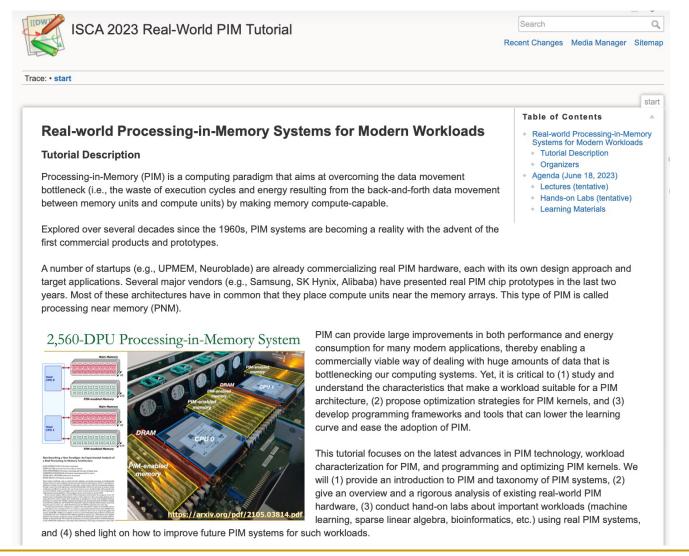

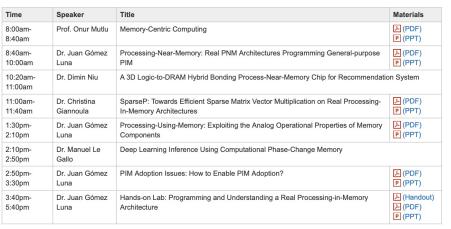

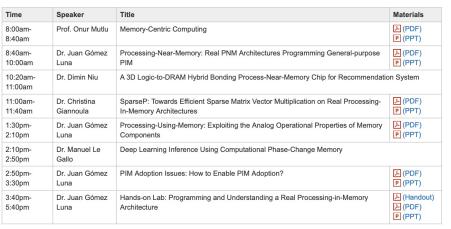

#### Real PIM Tutorials [ISCA'23, ASPLOS'23, HPCA'23]

June, March, Feb: Lectures + Hands-on labs + Invited talks

https://events.safari.ethz.ch/isca-pim-tutorial/

#### Real PIM Tutorial [ISCA 2023]

June 18: Lectures + Hands-on labs + Invited talks

#### **Tutorial Materials**

| Time                | Speaker                                | Title                                                                                                               | Materials                      |

|---------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------|

| 8:55am-<br>9:00am   | Dr. Juan Gómez Luna                    | Welcome & Agenda                                                                                                    | ▶(PDF) P(PPT)                  |

| 9:00am-<br>10:20am  | Prof. Onur Mutlu                       | Memory-Centric Computing                                                                                            | ▶(PDF) P(PPT)                  |

| 10:20am-<br>11:00am | Dr. Juan Gómez Luna                    | Processing-Near-Memory: Real PNM Architectures / Programming General-purpose PIM                                    | ▶(PDF) P(PPT)                  |

| 11:20am-<br>11:50am | Prof. Izzat El Hajj                    | High-throughput Sequence Alignment using Real Processing-in-Memory Systems                                          | ▶(PDF) P(PPT)                  |

| 11:50am-<br>12:30pm | Dr. Christina Giannoula                | SparseP: Towards Efficient Sparse Matrix Vector Multiplication for Real Processing-In-Memory Systems                | ▶(PDF) P(PPT)                  |

| 2:00pm-<br>2:45pm   | Dr. Sukhan Lee                         | Introducing Real-world HBM-PIM Powered System for Memory-bound Applications                                         | (PDF) (PPT)                    |

| 2:45pm-<br>3:30pm   | Dr. Juan Gómez Luna /<br>Ataberk Olgun | Processing-Using-Memory: Exploiting the Analog Operational Properties of Memory Components / PUM Prototypes: PiDRAM | ▶(PDF) P(PPT)<br>▶(PDF) P(PPT) |

| 4:00pm-<br>4:40pm   | Dr. Juan Gómez Luna                    | Accelerating Modern Workloads on a General-purpose PIM System                                                       | ▶(PDF) P(PPT)                  |

| 4:40pm-<br>5:20pm   | Dr. Juan Gómez Luna                    | Adoption Issues: How to Enable PIM?                                                                                 | ▶(PDF) P(PPT)                  |

| 5:20pm-<br>5:30pm   | Dr. Juan Gómez Luna                    | Hands-on Lab: Programming and Understanding a Real Processing-in-<br>Memory Architecture                            | → (Handout)  → (PDF)  P (PPT)  |

https://www.youtube.com/ live/GIb5EgSrWk0

https://events.safari.ethz.ch/ isca-pim-tutorial/

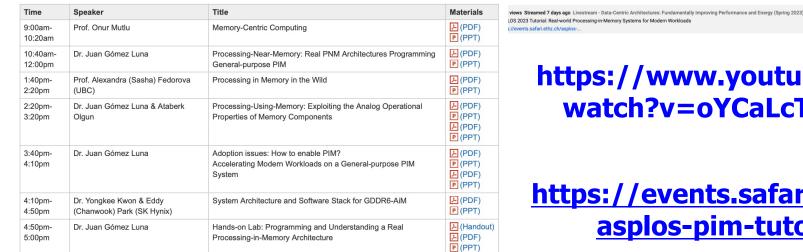

#### Real PIM Tutorial [ASPLOS 2023]

#### March 26: Lectures + Hands-on labs + Invited talks

Onur Mutlu Lectures

32.1K subscribers

↑ Subscribed ∨

views Streamed 7 days ago Livestream - Data-Centric Architectures: Fundamentally Improving Performance and Energy (Spring 2023)

#### **Tutorial Materials**

| Time                | Speaker                                               | Title                                                                                             | Materials                          | views Streamed 7 days ago Livestream - Data-Centric Architectures: Fundamentally In                              |

|---------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------|

| 9:00am-<br>10:20am  | Prof. Onur Mutlu                                      | Memory-Centric Computing                                                                          | ♪ (PDF) P (PPT)                    | LOS 2023 Tutorial: Real-world Processing-in-Memory Systems for Modern Workloads :://events.safari.ethz.ch/asplos |

| 10:40am-<br>12:00pm | Dr. Juan Gómez Luna                                   | Processing-Near-Memory: Real PNM Architectures Programming General-purpose PIM                    | P (PPT)                            |                                                                                                                  |

| 1:40pm-<br>2:20pm   | Prof. Alexandra (Sasha) Fedorova (UBC)                | Processing in Memory in the Wild                                                                  | → (PDF) P (PPT)                    | https://www                                                                                                      |

| 2:20pm-<br>3:20pm   | Dr. Juan Gómez Luna & Ataberk<br>Olgun                | Processing-Using-Memory: Exploiting the Analog Operational Properties of Memory Components        | P(PDF) P(PPT) P(PPT)               | watch?v=                                                                                                         |

| 3:40pm-<br>4:10pm   | Dr. Juan Gómez Luna                                   | Adoption issues: How to enable PIM? Accelerating Modern Workloads on a General-purpose PIM System | → (PDF)  P (PPT)  → (PDF)  P (PPT) | https://avan                                                                                                     |

| 4:10pm-<br>4:50pm   | Dr. Yongkee Kwon & Eddy<br>(Chanwook) Park (SK Hynix) | System Architecture and Software Stack for GDDR6-AiM                                              | P (PDF)                            | https://ever                                                                                                     |

| 4:50pm-<br>5:00pm   | Dr. Juan Gómez Luna                                   | Hands-on Lab: Programming and Understanding a Real<br>Processing-in-Memory Architecture           |                                    | asplos-                                                                                                          |

https://www.youtube.com/ watch?v=oYCaLcT0Kmo

https://events.safari.ethz.ch/ asplos-pim-tutorial/

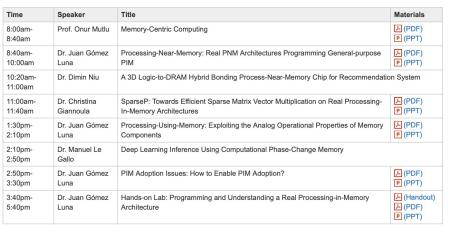

#### Real PIM Tutorial [HPCA 2023]

#### February 26: Lectures + Hands-on labs + Invited Talks

https://www.youtube.com/

watch?v=f5-nT1tbz5w

https://events.safari.ethz.ch/ real-pim-tutorial/

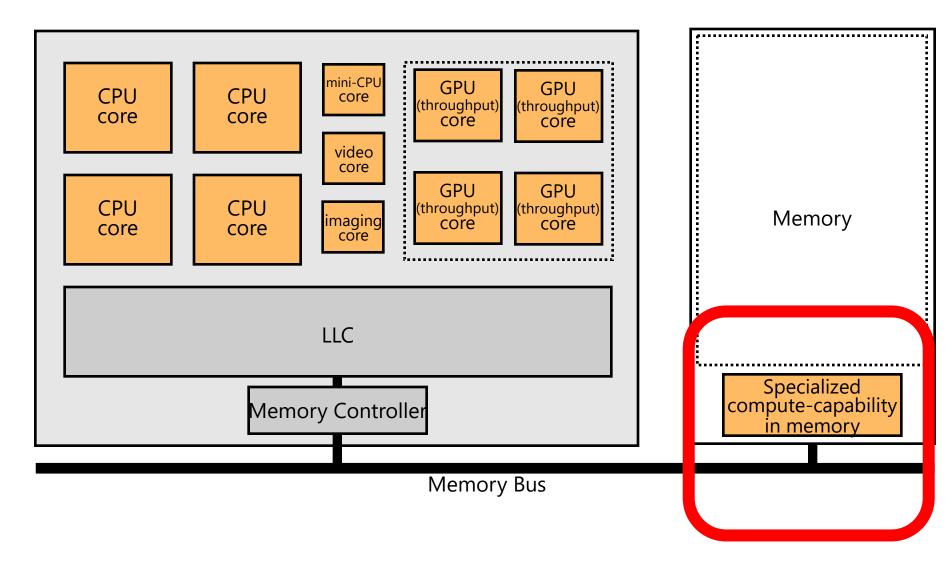

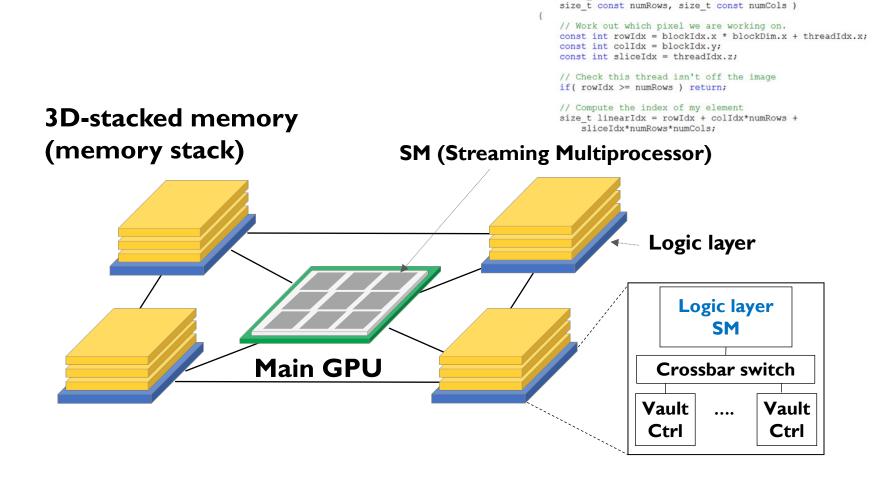

# We Need to Think Differently from the Past Approaches

# Processing in Memory: Two Approaches

- 1. Processing using Memory

- 2. Processing near Memory

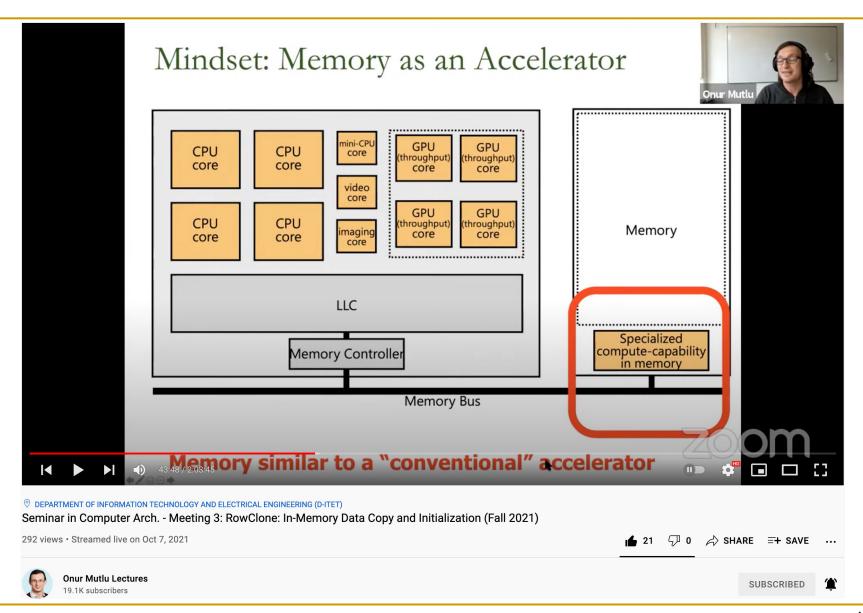

## Mindset: Memory as an Accelerator

Memory similar to a "conventional" accelerator

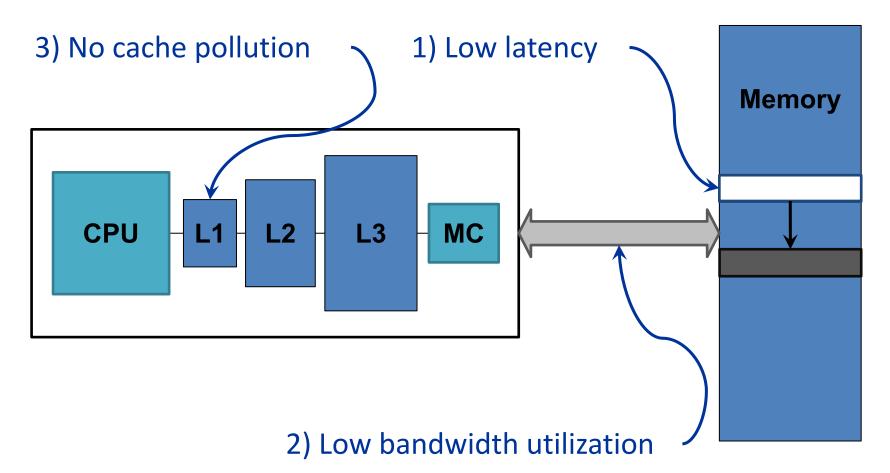

## Starting Simple: Data Copy and Initialization

memmove & memcpy: 5% cycles in Google's datacenter [Kanev+ISCA'15]

Zero initialization (e.g., security)

**Page Migration**

## Future Systems: In-Memory Copy

4) No unwanted data movement

1046ns, 3.6uJ → 90ns, 0.04uJ

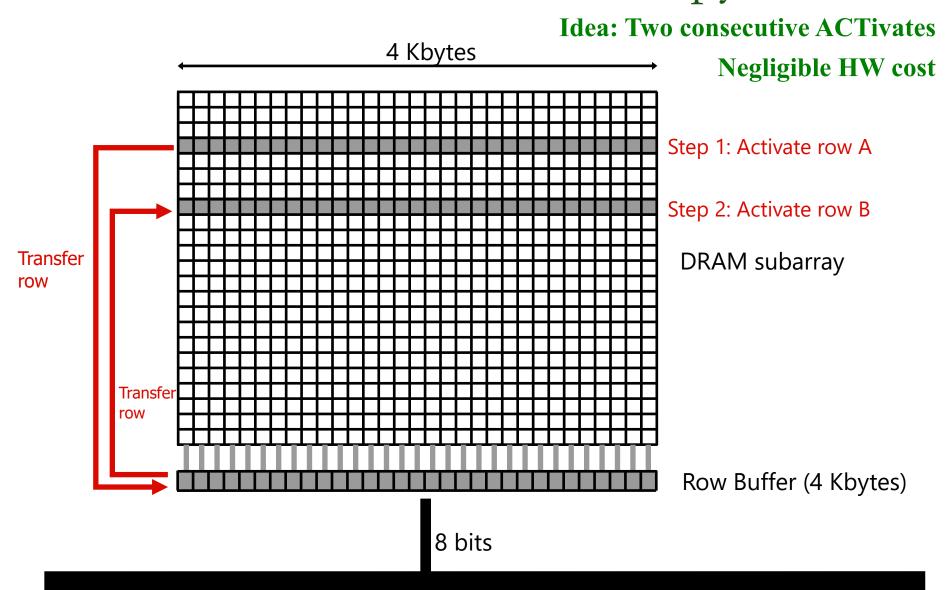

## RowClone: In-DRAM Row Copy

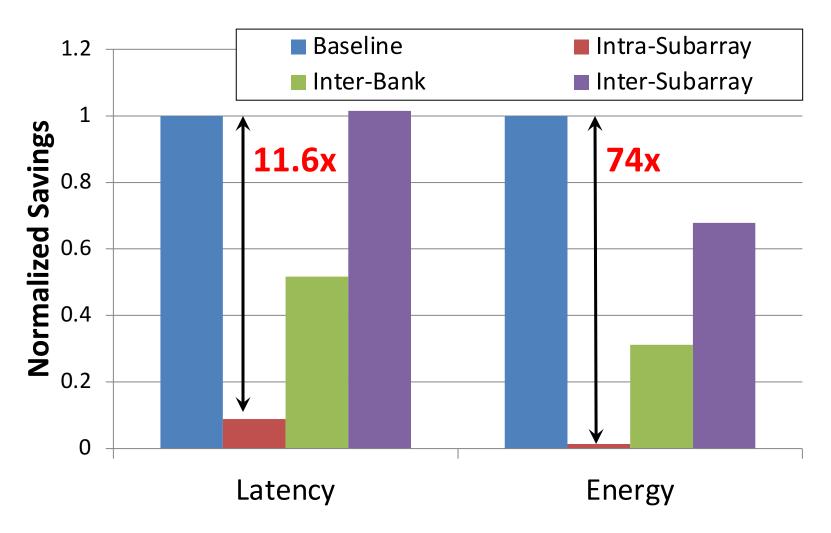

## RowClone: Latency and Energy Savings

Seshadri et al., "RowClone: Fast and Efficient In-DRAM Copy and Initialization of Bulk Data," MICRO 2013.

### More on RowClone

Vivek Seshadri, Yoongu Kim, Chris Fallin, Donghyuk Lee, Rachata

Ausavarungnirun, Gennady Pekhimenko, Yixin Luo, Onur Mutlu, Michael A.

Kozuch, Phillip B. Gibbons, and Todd C. Mowry,

"RowClone: Fast and Energy-Efficient In-DRAM Bulk Data Copy and Initialization"

Proceedings of the <u>46th International Symposium on Microarchitecture</u> (**MICRO**), Davis, CA, December 2013. [<u>Slides (pptx) (pdf)</u>] [<u>Lightning Session Slides (pptx) (pdf)</u>] [<u>Poster (pptx) (pdf)</u>]

# RowClone: Fast and Energy-Efficient In-DRAM Bulk Data Copy and Initialization

Vivek Seshadri Yoongu Kim Chris Fallin\* Donghyuk Lee vseshadr@cs.cmu.edu yoongukim@cmu.edu cfallin@c1f.net donghyuk1@cmu.edu

Rachata Ausavarungnirun Gennady Pekhimenko Yixin Luo rachata@cmu.edu gpekhime@cs.cmu.edu yixinluo@andrew.cmu.edu

Onur Mutlu Phillip B. Gibbons† Michael A. Kozuch† Todd C. Mowry onur@cmu.edu phillip.b.gibbons@intel.com michael.a.kozuch@intel.com tcm@cs.cmu.edu

Carnegie Mellon University †Intel Pittsburgh

## RowClone in Off-the-Shelf DRAM Chips

Idea: Violate DRAM timing parameters to mimic RowClone

## ComputeDRAM: In-Memory Compute Using Off-the-Shelf DRAMs

Fei Gao feig@princeton.edu Department of Electrical Engineering Princeton University Georgios Tziantzioulis georgios.tziantzioulis@princeton.edu Department of Electrical Engineering Princeton University David Wentzlaff

wentzlaf@princeton.edu

Department of Electrical Engineering

Princeton University

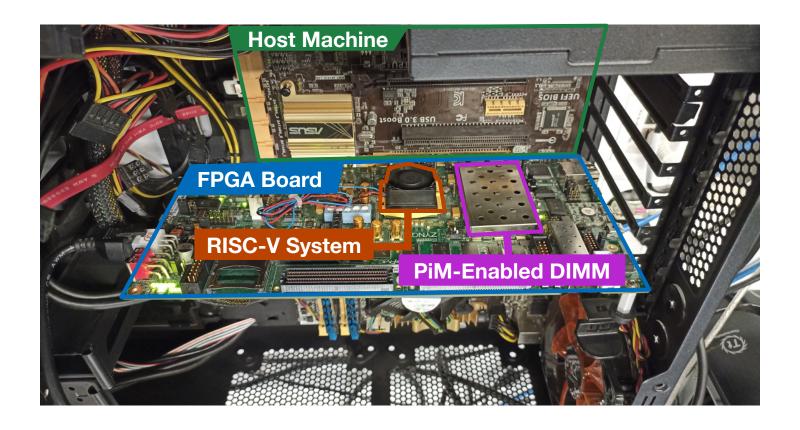

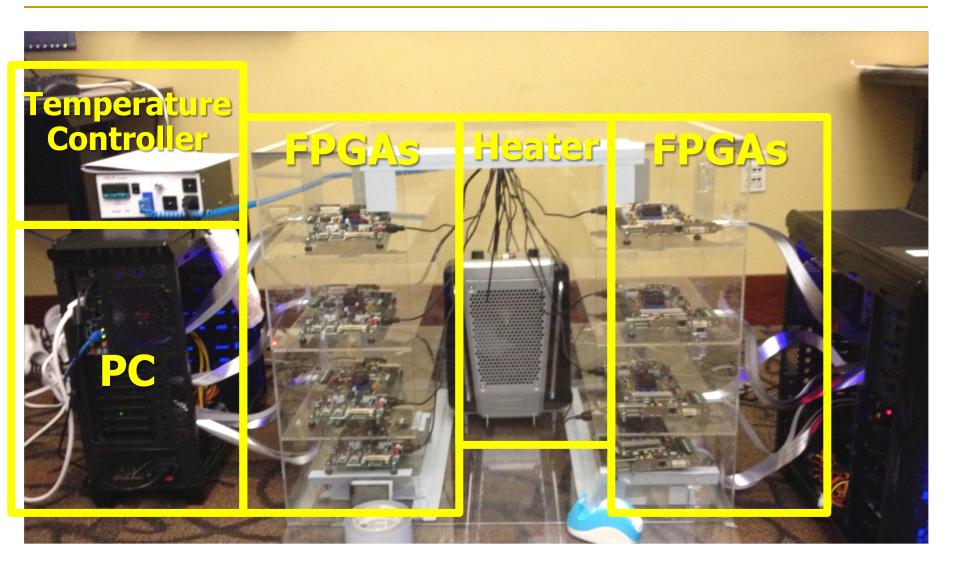

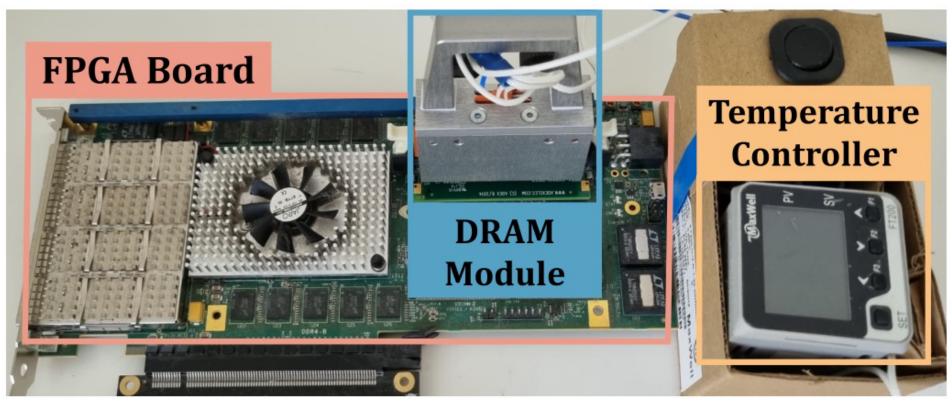

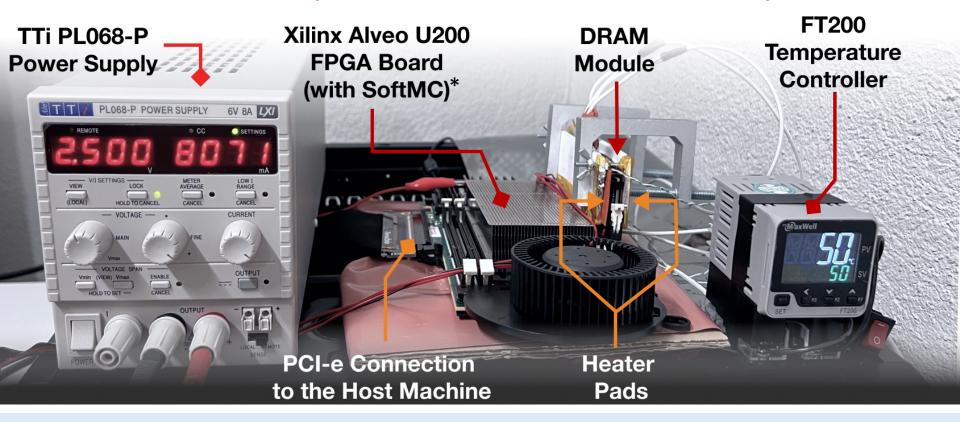

## Real Processing Using Memory Prototype

- End-to-end RowClone & TRNG using off-the-shelf DRAM chips

- Idea: Violate DRAM timing parameters to mimic RowClone

# PiDRAM: A Holistic End-to-end FPGA-based Framework for Processing-in-DRAM

Ataberk Olgun<sup>§†</sup> Juan Gómez Luna<sup>§</sup> Hasan Hassan<sup>§</sup>

Konstantinos Kanellopoulos<sup>§</sup> Oğuz Ergin<sup>†</sup> Onur Mutlu<sup>§</sup> Behzad Salami§\*

§ETH Zürich

†TOBB ETÜ

\*BSC

https://arxiv.org/pdf/2111.00082.pdf

https://github.com/cmu-safari/pidram

https://www.youtube.com/watch?v=qeukNs5XI3g&t=4192s

## Real Processing-using-Memory Prototype

https://arxiv.org/pdf/2111.00082.pdf

https://github.com/cmu-safari/pidram

https://www.youtube.com/watch?v=qeukNs5XI3g&t=4192s

## Real Processing-using-Memory Prototype

https://arxiv.org/pdf/2111.00082.pdf https://github.com/cmu-safari/pidram

https://www.youtube.com/watch?v=qeukNs5XI3g&t=4192s

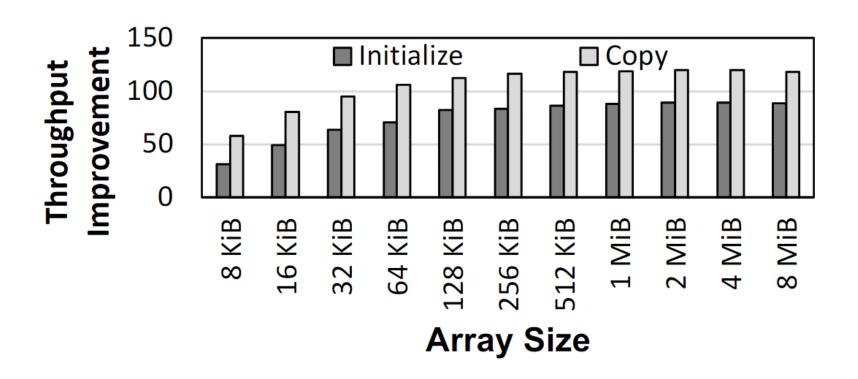

### Microbenchmark Copy/Initialization Throughput

In-DRAM Copy and Initialization improve throughput by 119x and 89x

### More on PiDRAM

Ataberk Olgun, Juan Gomez Luna, Konstantinos Kanellopoulos, Behzad Salami, Hasan Hassan, Oguz Ergin, and Onur Mutlu,

"PiDRAM: A Holistic End-to-end FPGA-based Framework for Processing-in-DRAM"

<u>ACM Transactions on Architecture and Code Optimization</u> (**TACO**), March 2023. [arXiv version]

Presented at the 18th HiPEAC Conference, Toulouse, France, January 2023.

[Slides (pptx) (pdf)]

[Longer Lecture Slides (pptx) (pdf)]

[Lecture Video (40 minutes)]

[PiDRAM Source Code]

# PiDRAM: A Holistic End-to-end FPGA-based Framework for <u>Processing-in-DRAM</u>

Ataberk Olgun§ Juan Gómez Luna§ Konstantinos Kanellopoulos§ Behzad Salami§ Hasan Hassan§ Oğuz Ergin† Onur Mutlu§

§ETH Zürich †TOBB University of Economics and Technology

### Lecture on RowClone & Processing using DRAM

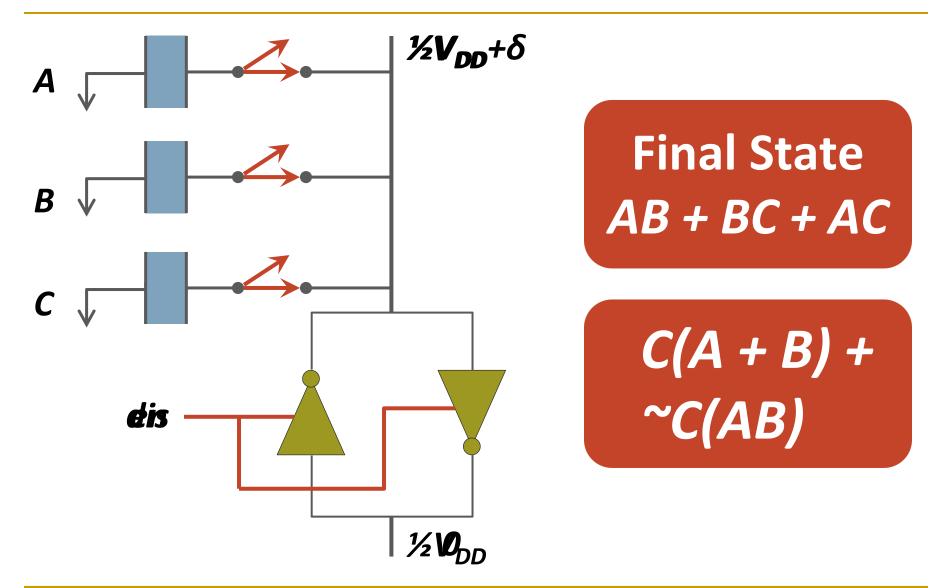

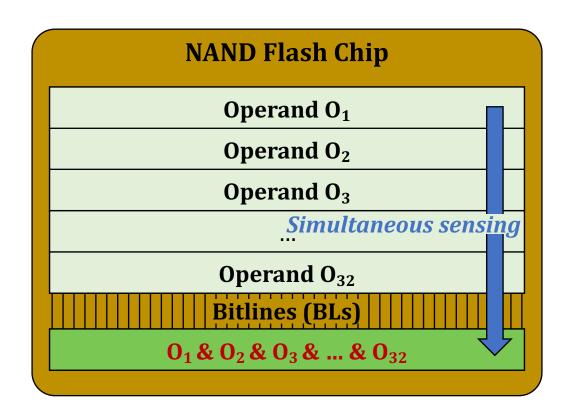

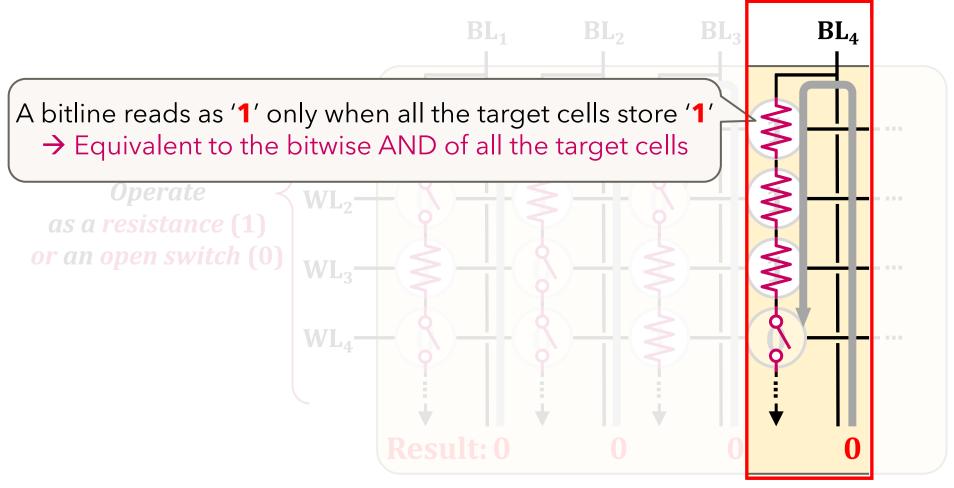

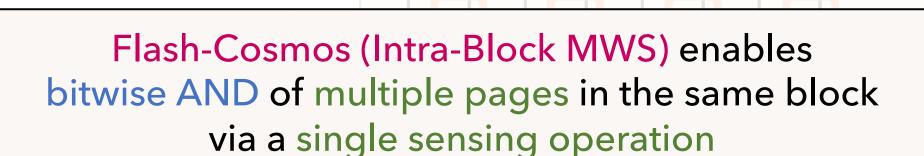

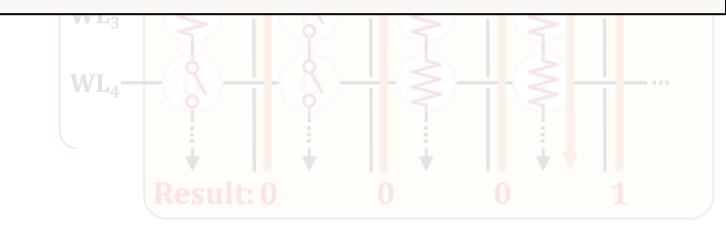

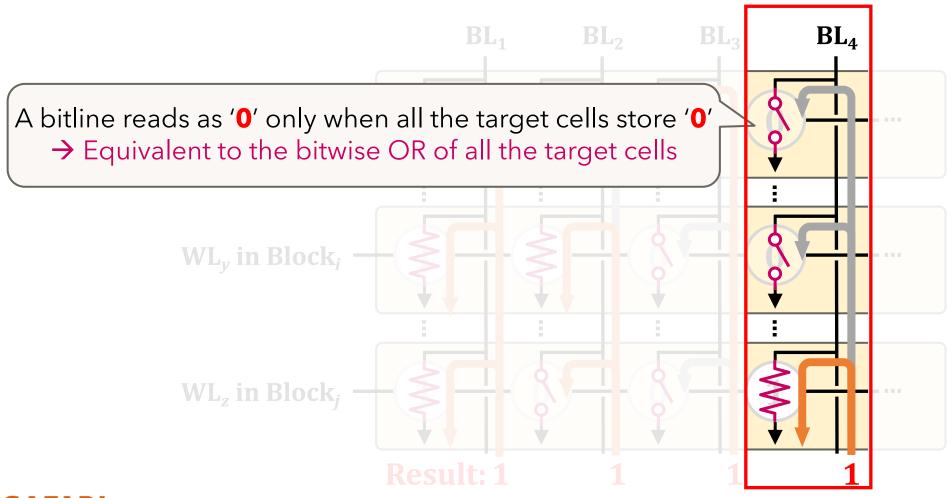

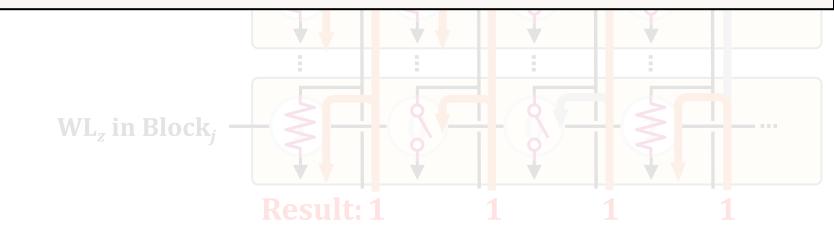

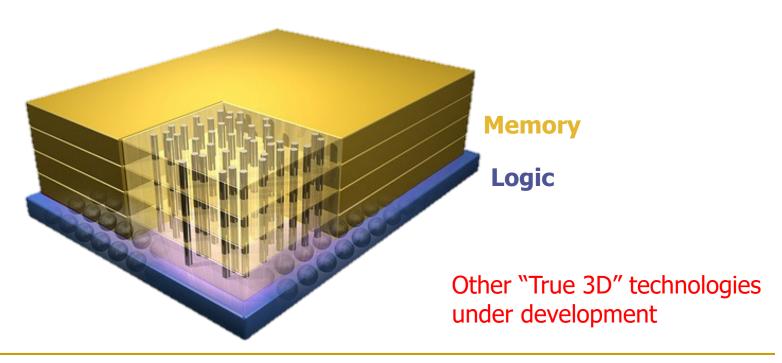

## (Truly) In-Memory Computation

- We can support in-DRAM AND, OR, NOT, MAJ

- At low cost

- Using analog computation capability of DRAM

- Idea: activating multiple rows performs computation

- 30-60X performance and energy improvement

- Seshadri+, "Ambit: In-Memory Accelerator for Bulk Bitwise Operations Using Commodity DRAM Technology," MICRO 2017.

- New memory technologies enable even more opportunities

- Memristors, resistive RAM, phase change mem, STT-MRAM, ...

- Can operate on data with minimal movement

### In-DRAM AND/OR: Triple Row Activation

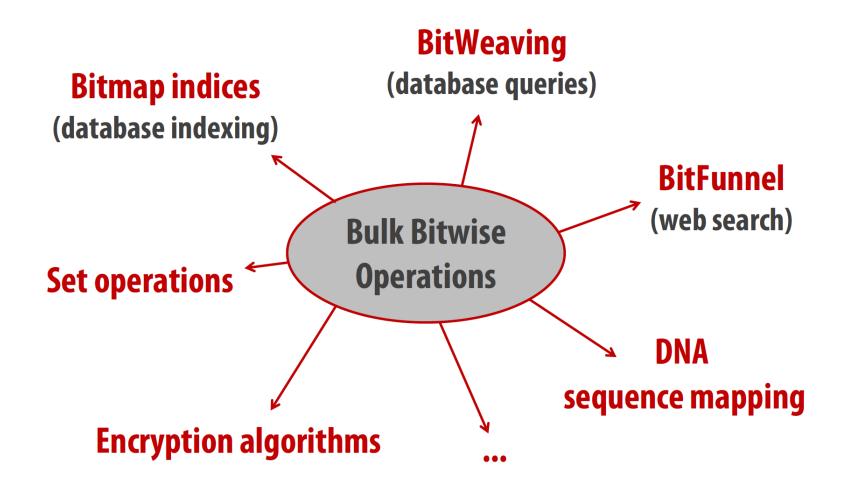

### Bulk Bitwise Operations in Workloads

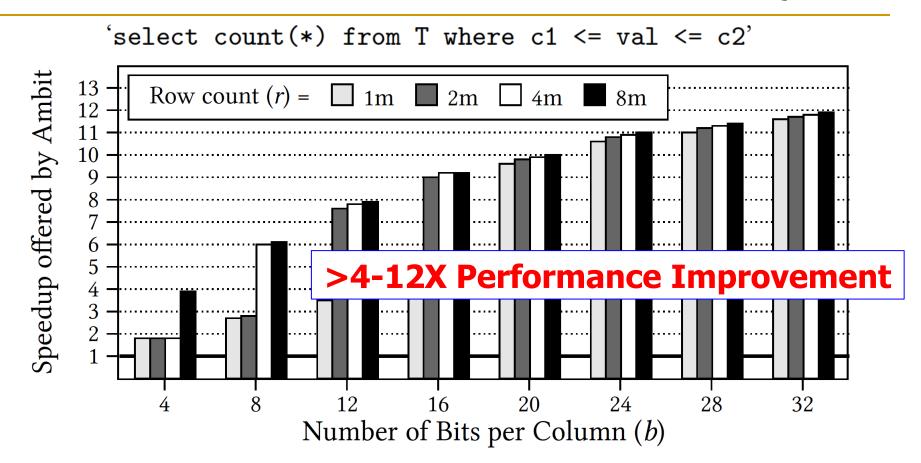

### In-DRAM Acceleration of Database Queries

Figure 11: Speedup offered by Ambit over baseline CPU with SIMD for BitWeaving

Seshadri+, "Ambit: In-Memory Accelerator for Bulk Bitwise Operations using Commodity DRAM Technology," MICRO 2017.

### More on Ambit

Vivek Seshadri, Donghyuk Lee, Thomas Mullins, Hasan Hassan, Amirali Boroumand, Jeremie Kim, Michael A. Kozuch, Onur Mutlu, Phillip B. Gibbons, and Todd C. Mowry,

"Ambit: In-Memory Accelerator for Bulk Bitwise Operations Using Commodity DRAM Technology"

Proceedings of the <u>50th International Symposium on</u>

<u>Microarchitecture</u> (**MICRO**), Boston, MA, USA, October 2017.

[Slides (pptx) (pdf)] [Lightning Session Slides (pptx) (pdf)] [Poster (pptx) (pdf)]

Ambit: In-Memory Accelerator for Bulk Bitwise Operations

Using Commodity DRAM Technology

Vivek Seshadri<sup>1,5</sup> Donghyuk Lee<sup>2,5</sup> Thomas Mullins<sup>3,5</sup> Hasan Hassan<sup>4</sup> Amirali Boroumand<sup>5</sup> Jeremie Kim<sup>4,5</sup> Michael A. Kozuch<sup>3</sup> Onur Mutlu<sup>4,5</sup> Phillip B. Gibbons<sup>5</sup> Todd C. Mowry<sup>5</sup>

$^1$ Microsoft Research India  $^2$ NVIDIA Research  $^3$ Intel  $^4$ ETH Zürich  $^5$ Carnegie Mellon University

### In-DRAM Bulk Bitwise Execution

Vivek Seshadri and Onur Mutlu,

"In-DRAM Bulk Bitwise Execution Engine"

Invited Book Chapter in Advances in Computers, to appear in 2020.

[Preliminary arXiv version]

### In-DRAM Bulk Bitwise Execution Engine

Vivek Seshadri Microsoft Research India visesha@microsoft.com Onur Mutlu

ETH Zürich

onur.mutlu@inf.ethz.ch

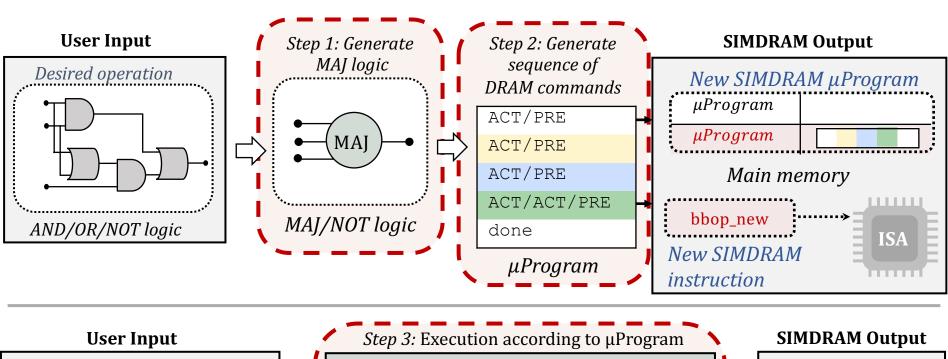

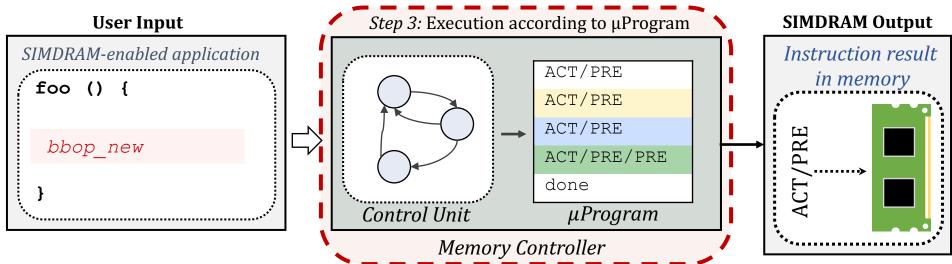

### SIMDRAM Framework

Nastaran Hajinazar, Geraldo F. Oliveira, Sven Gregorio, Joao Dinis Ferreira, Nika Mansouri Ghiasi, Minesh Patel, Mohammed Alser, Saugata Ghose, Juan Gomez-Luna, and Onur Mutlu, "SIMDRAM: An End-to-End Framework for Bit-Serial SIMD Computing in DRAM" Proceedings of the 26th International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS), Virtual, March-April 2021.

[2-page Extended Abstract]

[Short Talk Slides (pptx) (pdf)]

[Talk Slides (pptx) (pdf)]

[Short Talk Video (5 mins)]

[Full Talk Video (27 mins)]

# SIMDRAM: A Framework for Bit-Serial SIMD Processing using DRAM

\*Nastaran Hajinazar<sup>1,2</sup>

Nika Mansouri Ghiasi<sup>1</sup>

\*Geraldo F. Oliveira<sup>1</sup>

Minesh Patel<sup>1</sup>

Iuan Gómez-Luna<sup>1</sup>

Sven Gregorio<sup>1</sup> Mohammed Alser<sup>1</sup> Onur Mutlu<sup>1</sup>

João Dinis Ferreira<sup>1</sup> Saugata Ghose<sup>3</sup>

<sup>1</sup>ETH Zürich

<sup>2</sup>Simon Fraser University

<sup>3</sup>University of Illinois at Urbana-Champaign

### **SIMDRAM Framework: Overview**

SAFARI

## **SIMDRAM Key Results**

#### Evaluated on:

- 16 complex in-DRAM operations

- 7 commonly-used real-world applications

#### **SIMDRAM** provides:

- 88× and 5.8× the throughput of a CPU and a high-end GPU, respectively, over 16 operations

- 257× and 31× the energy efficiency of a CPU and a high-end GPU, respectively, over 16 operations

- 21× and 2.1× the performance of a CPU an a high-end GPU, over seven real-world applications

#### SAFARI

### More on SIMDRAM

Nastaran Hajinazar, Geraldo F. Oliveira, Sven Gregorio, Joao Dinis Ferreira, Nika Mansouri Ghiasi, Minesh Patel, Mohammed Alser, Saugata Ghose, Juan Gomez-Luna, and Onur Mutlu, "SIMDRAM: An End-to-End Framework for Bit-Serial SIMD Computing in DRAM" Proceedings of the 26th International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS), Virtual, March-April 2021.

[2-page Extended Abstract]

[Short Talk Slides (pptx) (pdf)]

[Talk Slides (pptx) (pdf)]

[Short Talk Video (5 mins)]

[Full Talk Video (27 mins)]

## SIMDRAM: A Framework for Bit-Serial SIMD Processing using DRAM

\*Nastaran Hajinazar<sup>1,2</sup>

Nika Mansouri Ghiasi<sup>1</sup>

\*Geraldo F. Oliveira<sup>1</sup>

Minesh Patel<sup>1</sup>

Juan Gómez-Luna<sup>1</sup>

Sven Gregorio<sup>1</sup> Mohammed Alser<sup>1</sup> Onur Mutlu<sup>1</sup> João Dinis Ferreira<sup>1</sup> Saugata Ghose<sup>3</sup>

<sup>1</sup>ETH Zürich

<sup>2</sup>Simon Fraser University

<sup>3</sup>University of Illinois at Urbana-Champaign

## In-DRAM Lookup-Table Based Execution

João Dinis Ferreira, Gabriel Falcao, Juan Gómez-Luna, Mohammed Alser, Lois Orosa, Mohammad Sadrosadati, Jeremie S. Kim, Geraldo F. Oliveira, Taha Shahroodi, Anant Nori, and Onur Mutlu, <u>"pLUTo: Enabling Massively Parallel Computation in DRAM via Lookup Tables"</u> Proceedings of the <u>55th International Symposium on Microarchitecture</u> (**MICRO**), Chicago, IL, USA,

[Slides (pptx) (pdf)]

[Longer Lecture Slides (pptx) (pdf)]

[Lecture Video (26 minutes)]

arXiv version

October 2022.

[Source Code (Officially Artifact Evaluated with All Badges)]

Officially artifact evaluated as available, reusable and reproducible.

#### pLUTo: Enabling Massively Parallel Computation in DRAM via Lookup Tables

João Dinis Ferreira§

Gabriel Falcao†

Juan Gómez-Luna§

Mohammed Alser§

Lois Orosa§∇

Mohammad Sadrosadati§

Jeremie S. Kim§

Geraldo F. Oliveira§

Taha Shahroodi‡

Anant Nori\*

Onur Mutlu§

§ETH Zürich

†IT, University of Coimbra  $\nabla$ Galicia Supercomputing Center

‡TU Delft

\*Intel

## In-DRAM Physical Unclonable Functions

Jeremie S. Kim, Minesh Patel, Hasan Hassan, and Onur Mutlu,

"The DRAM Latency PUF: Quickly Evaluating Physical Unclonable

Functions by Exploiting the Latency-Reliability Tradeoff in Modern DRAM Devices"

Proceedings of the <u>24th International Symposium on High-Performance Computer</u> <u>Architecture</u> (**HPCA**), Vienna, Austria, February 2018.

[Lightning Talk Video]

[Slides (pptx) (pdf)] [Lightning Session Slides (pptx) (pdf)]

[Full Talk Lecture Video (28 minutes)]

#### The DRAM Latency PUF:

Quickly Evaluating Physical Unclonable Functions by Exploiting the Latency-Reliability Tradeoff in Modern Commodity DRAM Devices

Jeremie S. Kim<sup>†§</sup> Minesh Patel<sup>§</sup> Hasan Hassan<sup>§</sup> Onur Mutlu<sup>§†</sup>

<sup>†</sup>Carnegie Mellon University <sup>§</sup>ETH Zürich

### In-DRAM True Random Number Generation

Jeremie S. Kim, Minesh Patel, Hasan Hassan, Lois Orosa, and Onur Mutlu,

"D-RaNGe: Using Commodity DRAM Devices to Generate True Random Numbers with Low Latency and High Throughput"

Proceedings of the <u>25th International Symposium on High-Performance Computer</u> <u>Architecture</u> (**HPCA**), Washington, DC, USA, February 2019.

[Slides (pptx) (pdf)]

[Full Talk Video (21 minutes)]

[Full Talk Lecture Video (27 minutes)]

Top Picks Honorable Mention by IEEE Micro.

### D-RaNGe: Using Commodity DRAM Devices to Generate True Random Numbers with Low Latency and High Throughput

Jeremie S. Kim<sup>‡§</sup> Minesh Patel<sup>§</sup> Hasan Hassan<sup>§</sup> Lois Orosa<sup>§</sup> Onur Mutlu<sup>§‡</sup>

<sup>‡</sup>Carnegie Mellon University <sup>§</sup>ETH Zürich

SAFARI 133

### In-DRAM True Random Number Generation

Ataberk Olgun, Minesh Patel, A. Giray Yaglikci, Haocong Luo, Jeremie S. Kim, F. Nisa Bostanci, Nandita Vijaykumar, Oguz Ergin, and Onur Mutlu,

"QUAC-TRNG: High-Throughput True Random Number Generation Using Quadruple Row Activation in Commodity DRAM Chips"

Proceedings of the <u>48th International Symposium on Computer Architecture</u> (**ISCA**), Virtual, June 2021.

[Slides (pptx) (pdf)]

[Short Talk Slides (pptx) (pdf)]

[Talk Video (25 minutes)]

[SAFARI Live Seminar Video (1 hr 26 mins)]

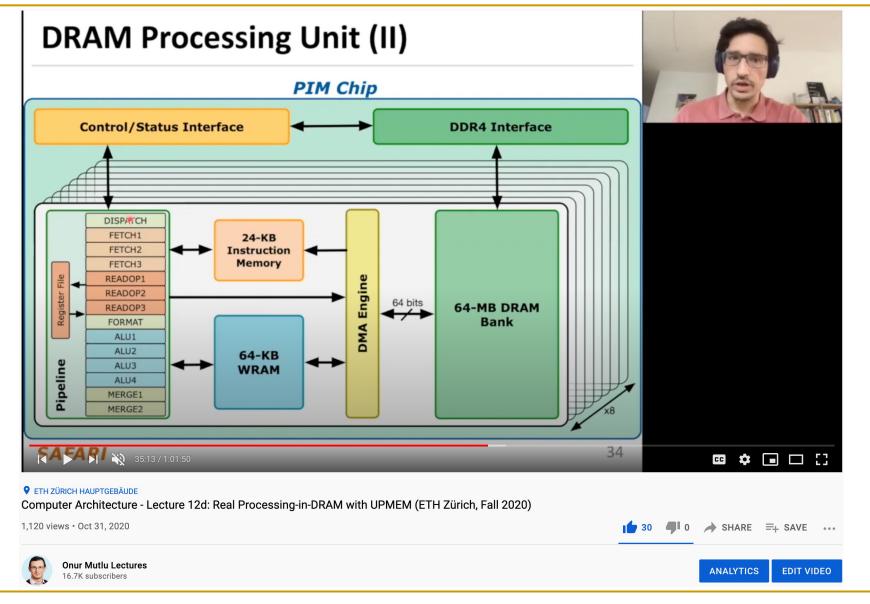

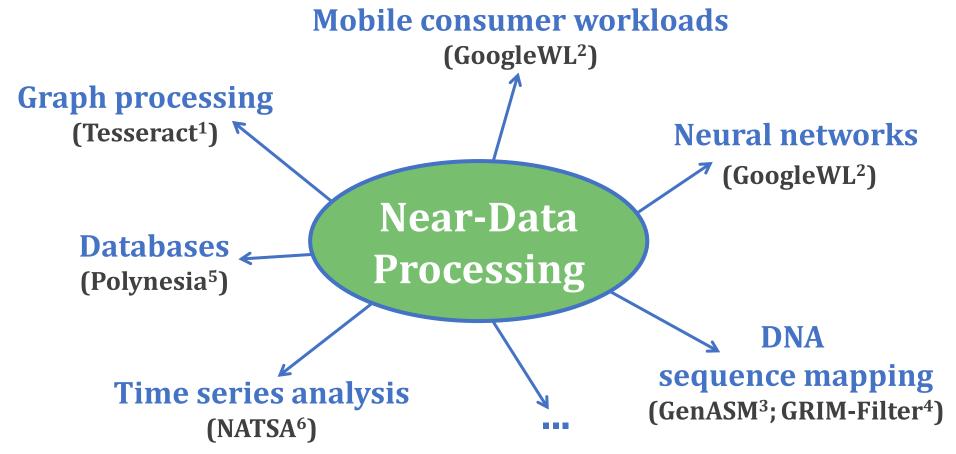

## QUAC-TRNG: High-Throughput True Random Number Generation Using Quadruple Row Activation in Commodity DRAM Chips