WISSENSCHAFTSRAT

WR

# **Efficient Associative Processing with RTM-TCAMs**

João Paulo C. de Lima, Asif Ali Khan, Hamid Farzaneh, <u>Jeronimo Castrillon</u> In-Memory Architectures and Computing Applications Workshop (iMACAW'23) Design Automation Conference (DAC'23). San Francisco, USA July 9, 2023

cfaed.tu-dresden.de

DRESDEN concept

### **Motivation**

# **Energy-efficiency** in CIM approaches comes from **reduced data-movement** and **massive parallelism**

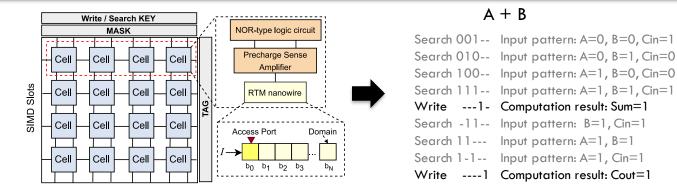

Associative Processors (APs) repurpose Content-Addressable Memories (CAMs) for SIMD tasks

#### 1. AP and multi-bit cells

APs cannot profit from multi-bit capability in ReRAMs

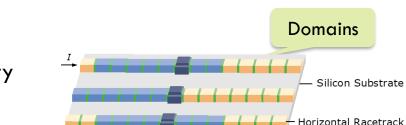

Why Racetrack Memories (RTMs) on APs?

APs are bitwise by nature, similar to RTMs

#### 2. Write frequency

- Intermediate results, e.g., carry signal, need frequent writes

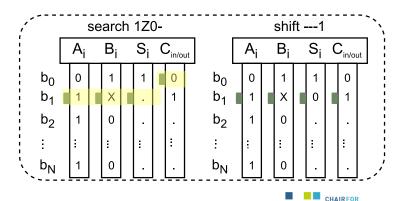

- RTMs' shift operation with pre-stored bits reduce the amount of writes

Access Ports

COMPILER

CONSTRUCTION

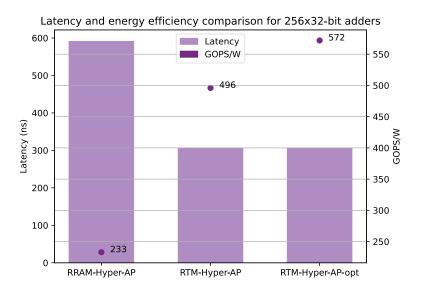

## **Preliminary results**

- Reduced number of bits for Cin/Cout signals

- Write operations for Cin/out replaced by less-costly shift operations

Reduced latency and improved energyefficiency under iso-area comparison

ADVANCING ELECTRONICS